What Is ASIC Design?

ASIC design is the process of developing a complex electronic system that can be fabricated into a special-purpose semiconductor device, typically for use in high-volume applications or those with stringent power, performance, and size constraints. System designers creating content for ASIC designs use high-level languages to develop and evaluate algorithms using simulation and visualization.

Many system designers use MATLAB® and Simulink® as high-level environments to specify algorithms for ASIC designs. By using these products in conjunction with third-party EDA tools, system designers can collaborate with ASIC hardware designers to model, simulate, optimize, and implement new algorithmic content for digital and analog/mixed-signal (AMS) ASIC designs using MATLAB and Simulink.

Modeling

You may choose to start ASIC design development using either MATLAB or Simulink to develop algorithms for hardware implementation. MATLAB provides a concise, untimed, language-based modeling environment, while the Simulink environment supports graphical modeling using multirate block diagrams, state machines, and other modeling constructs. MATLAB code can be incorporated into Simulink models, so there’s a smooth transition from MATLAB to a Simulink workflow.

Simulink models can be augmented for ASIC design by incorporating existing HDL code and simulating it using HDL cosimulation. Components from Mixed-Signal Blockset™ such as phase-locked loops (PLLs) and data converters (ADCs and DACs) may be added to evaluate interactions between analog and digital components.

Refining the ASIC Design Model for Code Generation

You then refine the ASIC design model with hardware implementation in mind. Algorithm developers can collaborate with ASIC hardware designers to optimize the hardware architecture of models. The first step is to review the MATLAB code or Simulink model to verify that it is suitable for HDL code generation. You can build models from more than 300 Simulink blocks and more than 200 MATLAB functions that can generate HDL code. The next step is to convert floating-point models to fixed point with Fixed-Point Designer™ to reduce the area and power consumption of designs. Simulink models can be further refined for ASIC designs by converting them from frame-based models to streaming models.

Model-Based Optimization for HDL Code Generation

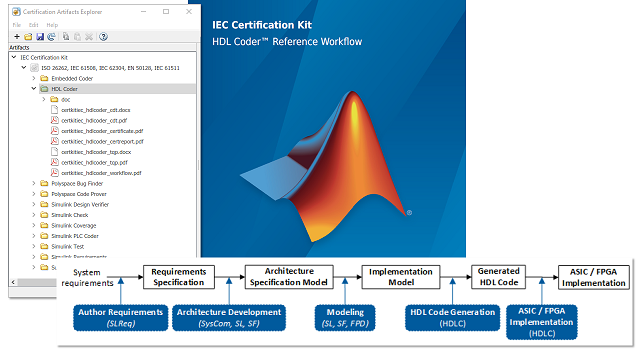

ASIC architectures provide many opportunities to optimize implementations in terms of power-performance-area (PPA). System designers can collaborate with ASIC hardware designers by using HDL Coder™ to generate synthesizable Verilog, SystemVerilog, and VHDL code from MATLAB code or Simulink models. HDL Coder provides a range of optimization options to help designers achieve the highest possible performance for their ASIC designs. These include automatic clock-rate optimization, resource sharing, and pipelining, which can significantly reduce the amount of logic required to implement a design. HDL Coder can support HDL code generation for multirate designs and triggered subsystems, as well.

HDL and SystemC Code Generation for ASIC Designs

Using HDL Coder, you can follow a guided workflow for the HDL code generation process for ASIC design. HDL Coder checks MATLAB and Simulink models for compatibility with HDL code generation, enables customization of the generated HDL code, produces presynthesis reports, and generates HDL testbenches. Further, HDL Coder integrates generated HDL with Cadence® Genus™ for ASIC synthesis.

You can generate synthesizable SystemC™ from MATLAB functions. The generated SystemC can serve as an input to the Cadence® Stratus™ High-Level Synthesis tool. Through the integration of Stratus HLS with the Genus logic synthesis solution and the Joules RTL power solution, ASIC designers get early visibility on the PPA of ASIC design implementations.

FPGA Prototyping for ASIC Designs

FPGA prototyping of ASIC designs is a popular method of evaluating algorithm implementations in ASIC verification. HDL Coder can generate scripts and projects for RTL synthesis and can integrate with synthesis and implementation tools from AMD, Altera, and Microchip to provide automated FPGA programming workflows. HDL Verifier™ enables you to insert logic to drive data into the FPGA or DDR memories from MATLAB using AXI Manager IP and to insert logic to capture data from signals internal to the FPGA for viewing and analysis in MATLAB.

For more information, see HDL Coder, HDL Verifier, Fixed-Point Designer, Mixed-Signal Blockset, and SerDes Toolbox™.

Examples and How To

Videos

Software Reference

See also: Embedded Systems, FPGA, ASIC, and SoC development, hardware design, high-level synthesis, VHDL testbench, mixed-signal systems, semiconductors, SoC architecture