Generieren von Tests

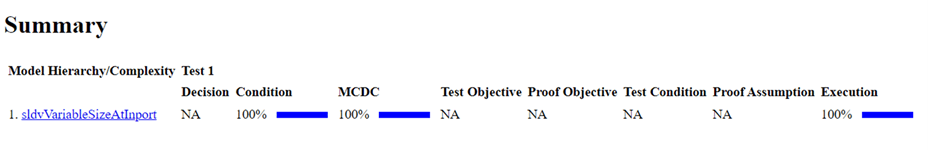

Simulink® Design Verifier™ generiert automatisch Testfälle, mit denen Sie das Modellverhalten umfassend bewerten können. Testfälle helfen Ihnen, die Modellleistung zu überprüfen, indem sie zeigen, wie die Blöcke im Modell in verschiedenen Modi ausgeführt werden. Bei der Generierung von Testfällen führt die Software eine formale Analyse Ihres Modells durch. Nach Abschluss der Analyse bietet Ihnen die Software verschiedene Möglichkeiten, die Ergebnisse zu überprüfen. Weitere Informationen finden Sie unter Generieren von Testfällen für ein Modell. Durch die Generierung von Testfällen unterstützt Simulink Design Verifier das Erreichen von Modellabdeckungszielen wie modifizierter Bedingungs-/Entscheidungsabdeckung (MC/DC) und Grenzwertanalyse. Diese Analyse erhöht nicht nur die Zuverlässigkeit des Modells, sondern beschleunigt auch den Verifikationsprozess, indem der manuelle Testaufwand reduziert wird. Die generierten Testfälle können verwendet werden, um das Modell anhand festgelegter Anforderungen zu validieren, die Einhaltung von Industriestandards sicherzustellen und das Risiko von Fehlern in späteren Entwicklungsphasen zu reduzieren.

Kategorien

- Grundlagen der Testgenerierung

Erstellen von Testfällen zur Validierung des Modellverhaltens

- Tests für funktionale Anforderungen

Validieren, ob das Simulink-modell den Anforderungen entspricht

- Tests für die Modellabdeckungsanalyse

Automatische Erstellung von Testfällen für eine gründliche Validierung

- Tests für die Codeabdeckungsanalyse

Bewertung der gründlichen Code-Validierung und -Zuverlässigkeit

- Tests für Subsysteme und referenzierte Modelle

Generieren von gezielten Testfällen zur Verifikation

- Realisieren einer lückenlosen Abdeckung

Identifizieren von Lücken und Erstellen umfassender Tests

- Verwendung des Tools und Verarbeitung der Ergebnisse

Verwendung des Tools zur Verbesserung der Modellverifikation