Erste Schritte in Simulink Design Verifier

Simulink® Design Verifier™ verwendet formale Methoden, um versteckte Konstruktionsfehler in Modellen zu identifizieren. Er erkennt Blöcke im Modell, die zu Ganzzahl-Überläufen, toter Logik, Array-Zugriffsverletzungen und Division durch Null führen. Es kann formell nachweisen, dass das Design die funktionalen Anforderungen erfüllt. Für jeden Designfehler oder jede Anforderungsverletzung wird ein Simulationstestfall zur Fehlersuche generiert.

Simulink Design Verifier generiert Testfälle für die Modellabdeckung und benutzerdefinierte Ziele, um bestehende anforderungsbasierte Testfälle zu erweitern. Diese Testfälle sorgen dafür, dass Ihr Modell die Bedingungen, Entscheidungen, modifizierten Bedingungen/Entscheidungen (MCDC) und benutzerdefinierten Abdeckungsziele erfüllt. Zusätzlich zu den Abdeckungszielen können Sie benutzerdefinierte Testziele festlegen, um automatisch anforderungsbasierte Testfälle zu generieren.

Unterstützung für Industriestandards ist über das IEC Certification Kit (for IEC 61508 and ISO 26262) und das DO Qualification Kit (for DO-178) verfügbar.

Tutorials

- Verwenden von Simulink Design Verifier für die systematische Modellverifikation

Erlernen der Grundlagen der Simulink Design Verifier-Analyse

- SCHRITT 1: Vorbereiten des Modells für die Testgenerierungsanalyse

- SCHRITT 2: Konfigurieren von Modelleinstellungen und Ausführen der Analyse

- SCHRITT 3: Überprüfen der Ergebnisse der Testgenerierungsanalyse

- SCHRITT 1: Vorbereiten des Modells für die Analyse zur Detektion von Designfehlern

- SCHRITT 2: Erkennen häufiger Designfehler

- SCHRITT 3: Durchführen einer Analyse zur Detektion von Designfehlern

- SCHRITT 4: Überprüfen der Ergebnisse der Designfehlerdetektion

- SCHRITT 5: Beheben von Designfehlern im Modell

Generieren von Testfällen für ein Modell

Bereiten Sie das Modell vor, konfigurieren Sie die Modelleinstellungen und überprüfen Sie die Ergebnisse der Testgenerierungsanalyse.

Erkennen von Designfehlern in einem Modell

Konfigurieren Sie die Modelleinstellungen, erkennen Sie Designfehler und überprüfen Sie die Ergebnisse.

Enthaltene Beispiele

Videos

Was ist Simulink Design Verifier?

Einführung in Simulink Design Verifier.

So verwenden Sie Simulink Design Verifier, um Designfehler in Ihren Simulink-Modellen automatisch zu erkennen

Verwenden Sie Simulink Design Verifier, um Fehler in einem Design zu finden und zu ermitteln, wie diese Fehler mithilfe der Visualisierungsfunktionen in Simulink Design Verifier behoben werden können.

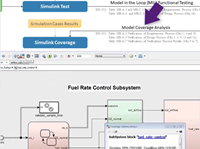

DO-178C-Workflow für die automatische Testvektorgenerierung

Verwenden Sie Simulink Design Verifier, um automatisch Testvektoren zu generieren, mit denen Sie die von Simulink Coverage erfassten fehlenden Modellabdeckungen analysieren können, um die Anforderungen von DO-178C und dessen Ergänzungen zu erfüllen.

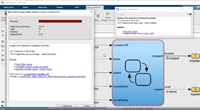

So debuggen Sie ein Gegenbeispiel für die Eigenschaftsprüfung

Die Eigenschaftsüberprüfung mit Simulink Design Verifier™ ist eine statische Analysetechnik, die formale Methoden verwendet, um zu überprüfen, ob eine bestimmte Eigenschaft immer gültig ist. Mit dieser Technik können Sie formell überprüfen, ob bestimmte Anforderungen, die in Ihrem Design implementiert sind, stets erfüllt werden.

Anforderungsbasierter Test-Workflow

Erläutert, wie Sie einen Test mithilfe einer Testsequenz erstellen, eine formale Bewertung definieren, Testfälle mit Anforderungen verknüpfen, Testsuiten ausführen und fehlende Modelltestabdeckung analysieren.