Überprüfen der Ergebnisse der Testgenerierungsanalyse

Überprüfen Sie die Analyseergebnisse, nachdem Simulink® Design Verifier™ die Analyse auf eine der folgenden Arten abgeschlossen hat:

Hervorheben von Ergebnissen im Modell.

Anzeigen eines Analyseberichts.

Überprüfen der Ergebnisse der Testgenerierungsanalyse

Führen Sie die ersten beiden Schritte dieses Tutorials aus, um eine Testgenerierungsanalyse durchzuführen, und überprüfen Sie anschließend die Ergebnisse.

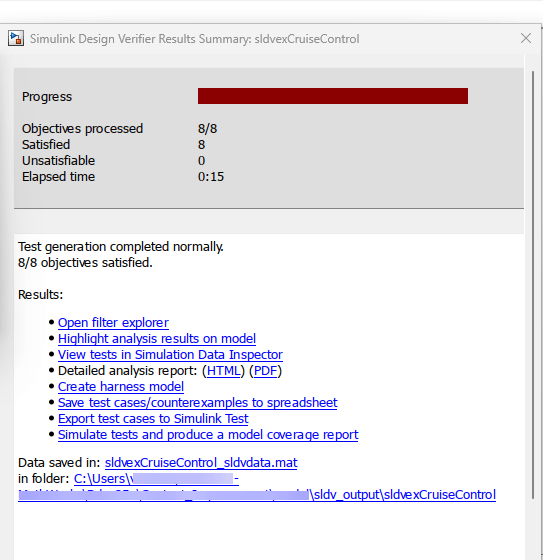

Wenn die Software die Analyse abgeschlossen hat, werden im Fenster „Results Summary“ Optionen zum Überprüfen der Ergebnisse angezeigt. Für jede Simulink Design Verifier-Analyse können Sie Aufgaben über das Fenster „Results Summary“ ausführen.

Alternativ können Sie auf der Registerkarte Design Verifier im Abschnitt Review Results auf Results Summary klicken, um die Ergebnisse anzuzeigen.

Solange Ihr Modell geöffnet ist, können Sie die Ergebnisse Ihrer letzten Simulink Design Verifier-Analyse im Fenster „Results Summary“ anzeigen.

Hervorhebung der Analyseergebnisse im Modell

Während der Analyse hebt Simulink Design Verifier die Modellobjekte automatisch hervor, wenn der Status der Ziele aktualisiert wird.

Um die Analyseergebnisse zum Modell sldvexCruiseControl hervorzuheben:

1. Klicken Sie im Fenster „Results Summary“ für die Analyse von sldvexCruiseControl auf Highlight analysis results on model.

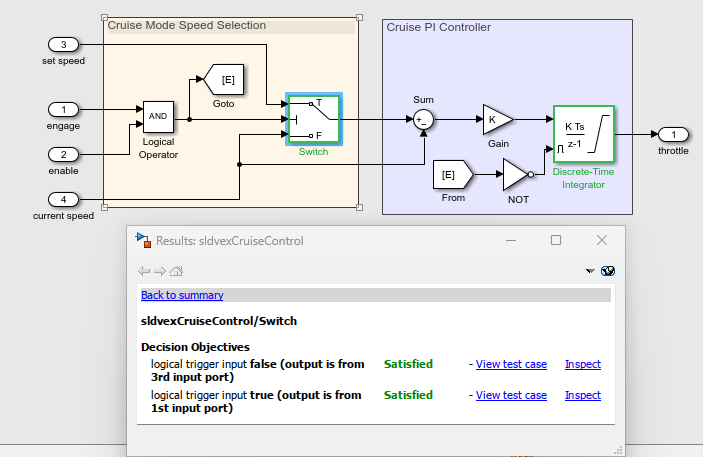

Der Switch-Block ist grün hervorgehoben, was darauf hinweist, dass der Switch-Block Testfälle enthält, die seine Testziele erfüllen.

2. Standardmäßig ist das Fenster „Simulink Design Verifier Results“ immer das oberste sichtbare Fenster. Um das Fenster hinter andere Fenster verschieben zu können, rechtsklicken Sie auf das Fenster und deaktivieren Sie Always on top. Wenn Sie auf Objekte im Modell klicken, wechselt dieses Fenster und zeigt detaillierte Analyseergebnisse für dieses Objekt an.

3. Klicken Sie auf den hervorgehobenen Switch-Block.

Die Zusammenfassung zeigt, dass alle Ziele des Switch-Blocks erfüllt sind. Klicken Sie ebenfalls auf den hervorgehobenen Block „Discrete-Time Integrator“, um die Analyseergebnisse für diesen Block im Fenster „Simulink Design Verifier Results“ anzuzeigen. Weitere Informationen zu hervorgehobenen Analyseergebnissen zu einem Modell finden Sie unter Highlight Results on the Model.

Überprüfen des detaillierten Analyseberichts

Klicken Sie im Fenster „Simulink Design Verifier Results Summary“ neben Detailed analysis report auf HTML. Der HTML-Bericht wird im MATLAB® Editor geöffnet.

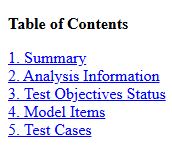

Der Bericht enthält das folgende Inhaltsverzeichnis.

Das Kapitel „Summary“ enthält Informationen zum Modell und zum Status der Ziele – erfüllt oder nicht erfüllt.

Das Kapitel „Analysis Information“ enthält Informationen zu folgenden Themen:

Das von Ihnen analysierte Modell.

Die Optionen, die Sie für die Analyse angegeben haben.

Die von der Software während der Analyse durchgeführten Annäherungen.

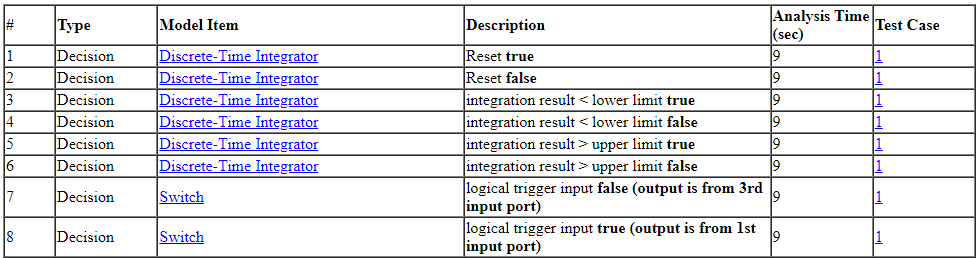

Das Kapitel „Test Objectives Status“ im HTML-Bericht enthält detaillierte Beschreibungen der erfüllten Ziele für jedes Modellelement und jeden generierten Testfall.

Klicken Sie in der Tabelle in der Spalte Test Case auf 1, um den Abschnitt „Test Case 1“ anzuzeigen.

Der Abschnitt „Test Objective Status“ im Bericht enthält Details zu einem Testfall, den die Analyse generiert hat, um ein Ziel in Ihrem Modell zu erreichen. Weitere Informationen zu HTML-Berichten finden Sie unter Review Results from Analysis Report.

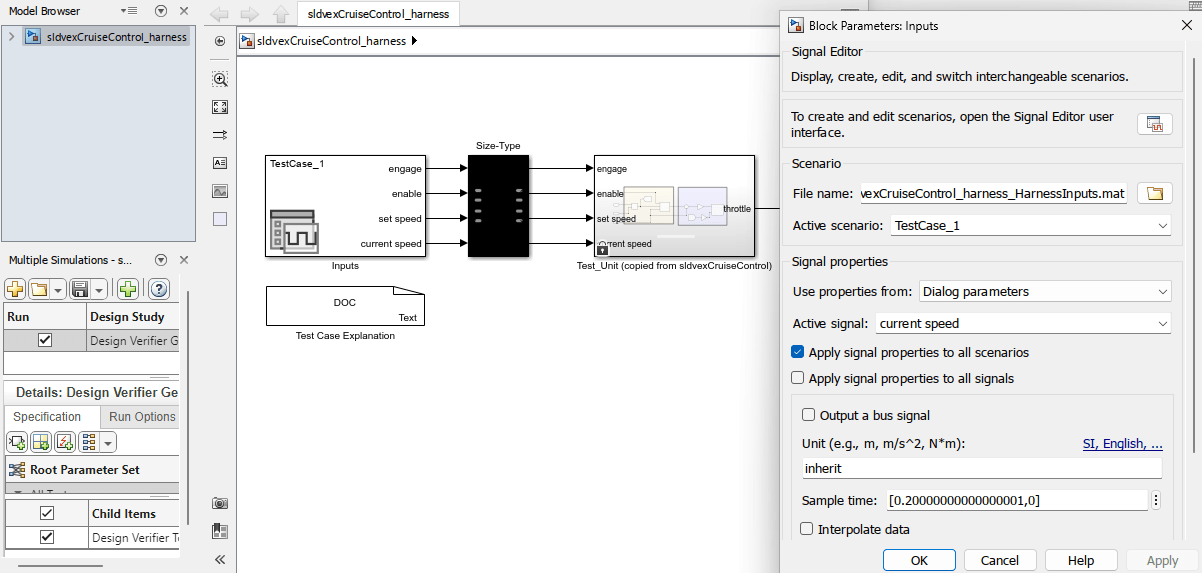

Überprüfen des Rahmenmodells

Um den Testfall für ein Modellabdeckungsziel anzuzeigen, klicken Sie im Fenster „Simulink Design Verifier Results“ auf View test case. Das Rahmenmodell sldvexCruiseControl_harness und der Signal Editor-Block werden geöffnet.

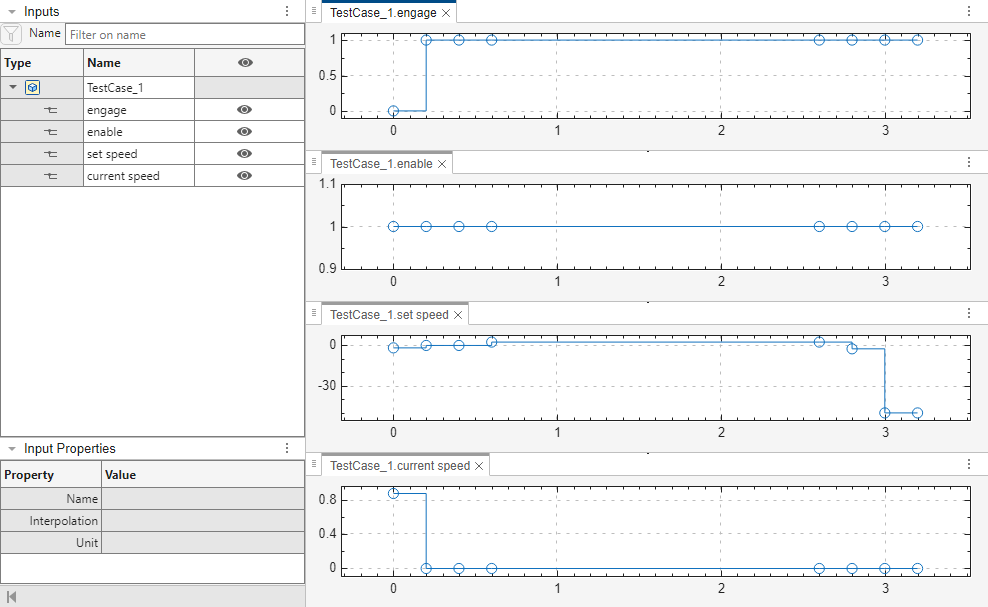

Der Signal Editor-Block mit dem Namen Inputs enthält die Testfälle. Doppelklicken Sie auf den Inputs-Block, um den Testfall anzuzeigen.

Hinweis: Bei großen Modellen kann die Analyse ein Rahmenmodell mit einer großen Anzahl von Testfällen erzeugen.

Um weniger Testfälle zu generieren, setzen Sie den Modellkonfigurationsparameter Test suite optimization auf LongTestcases und führen Sie die Analyse erneut aus.

Wenn Sie Test suite optimization auf LongTestcases setzen, generiert die Analyse weniger, dafür aber längere Testfälle, die jeweils mehrere Testziele erfüllen.

Simulieren des Testrahmenmodells und Erstellen eines Modellabdeckungsberichts

Simulieren Sie das Rahmenmodell mithilfe der generierten Testfälle im Rahmenmodell sldvexCruiseControl_harness .

Doppelklicken Sie im Rahmenmodell auf den Inputs-Block, um das Dialogfeld „Block Parameters“ zu öffnen, und klicken Sie dann auf die Schaltfläche „Open Signal Editor“, um das Fenster „Signal Editor“ zu öffnen.

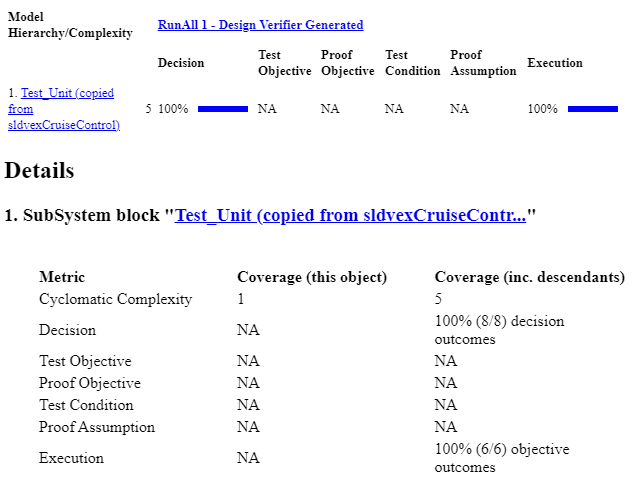

Klicken Sie im Modellrahmenfenster auf Run all.

Die Software simuliert das Rahmenmodell unter Verwendung beider Testfälle, sammelt Informationen zur Modellabdeckung und zeigt einen Abdeckungsbericht an. Der Abdeckungsbericht zeigt, dass die Testfälle eine Entscheidungsabdeckung von 100 % für das Modell sldvexCruiseControl aufweisen.

Sie können das Modell auch simulieren, ohne ein Rahmenmodell zu erstellen. Klicken Sie im Simulink Design Verifier-Protokollfenster auf Simulate tests and produce a model coverage report. Weitere Informationen zur Modellabdeckung finden Sie unter Top-Level Model Coverage Report (Simulink Coverage).

Weitere Informationen zum Rahmenmodell und zur Verwendung des Signal Editor-Blocks zur Erstellung eines Modellabdeckungsberichts finden Sie unter Use Harness Model for Test Simulations.

Anzeigen der sldvData-Datei

Die Simulink Design Verifier-Datendatei ist eine MAT-Datei, die eine Struktur mit dem Namen sldvData enthält. Diese Struktur speichert alle Daten, die während der Analyse erfasst und erzeugt werden. Sie können die Datendatei verwenden, um Ihre eigene Analyse durchzuführen oder einen benutzerdefinierten Bericht zu erstellen.

Um die Datendatei anzuzeigen, klicken Sie im Protokollfenster auf den Namen der Datendatei, in diesem Beispiel sldvexGenerateTestcasesExample_sldvdata.mat. Wenn Sie auf den Namen der Datendatei klicken, erstellt die Software eine Kopie des sldvData-Objekts im MATLAB-Workspace, sodass Sie die Daten überprüfen und bearbeiten können.

Weitere Informationen zu Simulink Design Verifier-Datendateien finden Sie unter View and Understand Analysis Results from Data Files.

Siehe auch

Workflow for Test Generation | Analyze Model and Interpret Results | Check Model Compatibility for Analysis | Highlight Results on the Model