Generieren von Testfällen für ein Modell

In Simulink® Design Verifier™ ist ein Testfall eine Reihe von Eingabewerten und den entsprechenden erwarteten Ausgaben, mit denen überprüft wird, ob sich ein Modell unter bestimmten Bedingungen wie vorgesehen verhält. Mit Simulink Design Verifier können Sie Testfälle für die Modellabdeckung und benutzerdefinierte Ziele erstellen. Sie können auch die Abdeckung bestehender anforderungsbasierter Testfälle messen und diese Testfälle erweitern, um die Abdeckung zu erhöhen oder eine vollständige Abdeckung zu erreichen.

Bevor Sie mit einer Analyse beginnen, führen Sie eine Kompatibilitätsprüfung Ihres Modells durch. Simulink Design Verifier analysiert das Modell nur, wenn es mit der Analyse kompatibel ist. Legen Sie nach der Kompatibilitätsprüfung die Einstellungen für die Testfallgenerierung im Modell fest und führen Sie die Analyse durch. Nachdem die Testgenerierungsanalyse abgeschlossen ist, überprüfen Sie die Ergebnisse.

Es gibt mehrere Möglichkeiten, die Analyseergebnisse zu überprüfen:

Überprüfen Sie die Analyseergebnisse auf einen Blick, indem Sie die Ergebnisse im Modell markieren.

Erstellen Sie ein Testrahmenmodell, um die Testfälle zu simulieren oder Gegenbeispiele zu debuggen.

Erstellen Sie einen Modellabdeckungsbericht.

Zeigen Sie die generierten Tests im Simulation Data Inspector an.

Erstellen Sie einen HTML- oder PDF-Bericht mit detaillierten Informationen zu den Analyseergebnissen.

Beispielmodell

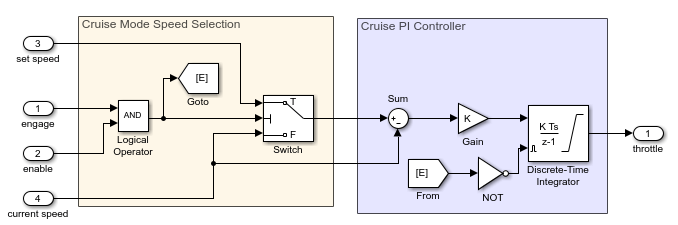

In diesem Tutorial wird ein vereinfachtes Tempomatmodell sldvexCruiseControl verwendet, das die Motordrosselklappe anpasst, um die vorgegebene Geschwindigkeit beizubehalten. Sie erstellen Testfälle, die die Abdeckungsziele für Bedingungen und Entscheidungsmodelle erfüllen, und simulieren diese Testfälle anschließend, um den Modellabdeckungsbericht zu erstellen.

Dieses Tempomatmodell sldvexCruiseControl erfüllt die folgenden Anforderungen:

Das Steuerungssystem wird aktiviert, wenn die Signale

engageundenableden Werttrueerreichen. Diese Bedingung wird durch den AND-Block definiert.Wenn das System aktiviert ist, leitet der Switch-Block den Wert

set speedan den PI-Regler weiter. Der PI-Regler berechnetthrottledurch Integration des durch die Differenzset speed - current speeddefinierten Fehlerterms.throttlewird so lange erhöht oder verringert, bisset speedgrößer alscurrent speedbzw. kleiner alscurrent speedist.Wenn das System nicht aktiviert ist, wird der Block Discrete-Time Integrator zurückgesetzt. Der Fehlerwert ist Null, was bedeutet, dass sich

throttlein der Rücksetzposition befindet.

Bei der Testgenerierungsanalyse generiert Simulink Design Verifier-Testfälle für die Modellabdeckungsziele, die mit jedem Modellelement im Modell verknüpft sind. Die Tabelle listet die Zustands- und Entscheidungsabdeckungsziele für die zugehörigen Modellblöcke auf.

| Block | Modellabdeckungsziel | Beschreibung des generierten Testfalls |

|---|---|---|

| AND | Zustand | Jeder Eingabewert wird unabhängig auf „true“ oder „false“ gesetzt. |

| NOT | Zustand | Die Eingabe wird unabhängig auf „true“ oder „false“ gesetzt. |

| Switch | Entscheidung | Der Testfall zeigt, dass Switch beide Eingabesignale an die Ausgabe weiterleitet. |

| Discrete-Time Integrator | Entscheidung |

|

In diesem Tutorial führen Sie eine Testgenerierungsanalyse für das Modell sldvexCruiseControl durch. Die Analyse generiert Testfälle, die die Bedingungen und Entscheidungsmodellabdeckungsziele erfüllen.

Sie werden Folgendes lernen:

Konfigurieren Sie die Modelleinstellungen für die Simulink Design Verifier-Analyse.

Überprüfen Sie die Modellkompatibilität für die Testgenerierungsanalyse.

Konfigurieren Sie das Modell, um Tests zu generieren und die Analyse durchzuführen.

Die Ergebnisse der Testgenerierungsanalyse anzeigen.

Rahmenmodell erstellen und Abdeckungsbericht generieren.

Um das Tutorial zu starten, siehe Vorbereiten des Modells für die Testgenerierungsanalyse.