Verwenden von Simulink Design Verifier für die systematische Modellverifikation

Steuerungsingenieure in der Automobil- und Luftfahrtindustrie müssen sicherstellen, dass die zugrunde liegenden Regelungsalgorithmen während des gesamten Betriebslebenszyklus das gewünschte Verhalten aufweisen.

Simulink® Design Verifier™ unterstützt Sie bei der systematischen Modellverifikation, um versteckte Designfehler zu identifizieren, Eigenschaften nachzuweisen und Testfälle für Funktionstests zu generieren. Simulink Design Verifier verwendet formale Verifikationsmethoden, um die Korrektheit des Designs zu überprüfen und das Vertrauen in Ihr Designmodell zu erhöhen, das für die Generierung des Produktionscodes verwendet wird. Beispielsweise können Ingenieure während des Entwicklungslebenszyklus Verifikationen und Validierungen durchführen, um sicherzustellen, dass:

das Motormanagementsystem während des Betriebs nicht zu unerwünschten Verhaltensweisen wie unbeabsichtigter Beschleunigung oder Motorabsterben führt.

Anwendungen für Fahrerassistenzsysteme (ADAS), die die Bremsen und die Lenkung steuern, unter allen Bedingungen einwandfrei funktionieren.

Autopilotsysteme auf alle möglichen Flugbedingungen und Eingaben korrekt reagieren.

Flugsteuerungssysteme stabil sind und schnell reagieren, um katastrophale Ausfälle während des Fluges zu verhindern.

Ein Modelldesigner und ein Testingenieur verwenden Simulink Design Verifier in der Entwicklungsphase des Modells, um die Verifikation und Validierung sicherzustellen.

Funktionen von Simulink Design Verifier

Simulink Design Verifier bietet unter anderem folgende Funktionen:

| Funktion | Beschreibung |

|---|---|

| Analysieren der funktionalen Anforderungen |

Weitere Informationen finden Sie unter Use Specification Models for Requirements-Based Testing. |

| Testgenerierung |

Weitere Informationen finden Sie unter Workflow for Test Generation. |

| Detektion von Designfehlern |

Weitere Informationen finden Sie unter What Is Design Error Detection?. |

| Nachweis von Eigenschaften |

Weitere Informationen finden Sie unter Prove Model Properties. |

| Inkrementelle Analyse, Filterung und Begründung |

|

Analyse des generierten Codes |

|

Zertifizierung oder Konformität | Erreichen der Compliance mit Industriestandards wie ISO 26262 für die Automobilindustrie oder DO-178C für die Luft- und Raumfahrt mithilfe der generierten Artefakte. |

So verwenden Sie Simulink Design Verifier

Die Verwendung von Simulink Design Verifier umfasst die folgenden wichtigen Schritte.

Modellvorbereitung: Bereiten Sie das Modell für die Analyse vor.

Wählen Sie den Analysemodus aus, z. B. Testfallgenerierung, Designfehlerdetektion oder Eigenschaftsnachweisanalyse.

Konfigurieren Sie die Analyseparameter und überprüfen Sie die Kompatibilität des Modells mit der Analyse. Weitere Informationen finden Sie unter Analyze Model and Interpret Results.

Konfigurieren von Modelleinstellungen und Ausführen von Analysen: Legen Sie die Modelleinstellungen fest und führen Sie die für Ihre Analyseanforderungen relevanten Analysen durch.

Wählen Sie die maximale Analysezeit, den Abdeckungsmodus, den Laufzeitfehlermodus, die Strategie und andere Konfigurationsparameter für die Analyse aus.

Führen Sie die Analyse durch.

Überprüfen der Ergebnisse: Zeigen Sie die generierten Ergebnisse an.

Überprüfen Sie die Ergebnisse des Modells, das nach Abschluss der Analyse mit Simulink Design Verifier markiert wurde.

Überprüfen Sie den Status der Ziele und legen Sie Folgemaßnahmen fest.

Erstellen Sie einen Analysebericht.

Exportieren der Ergebnisse: Nutzen Sie die aus den Ergebnissen gewonnenen Erkenntnisse, um das Modell oder die Analyseeinrichtung zu verfeinern.

Erstellen Sie einen Rahmen für die Simulation.

Exportieren Sie die Testfälle nach Simulink Test™.

Weitere Informationen finden Sie unter Analyze Model and Interpret Results.

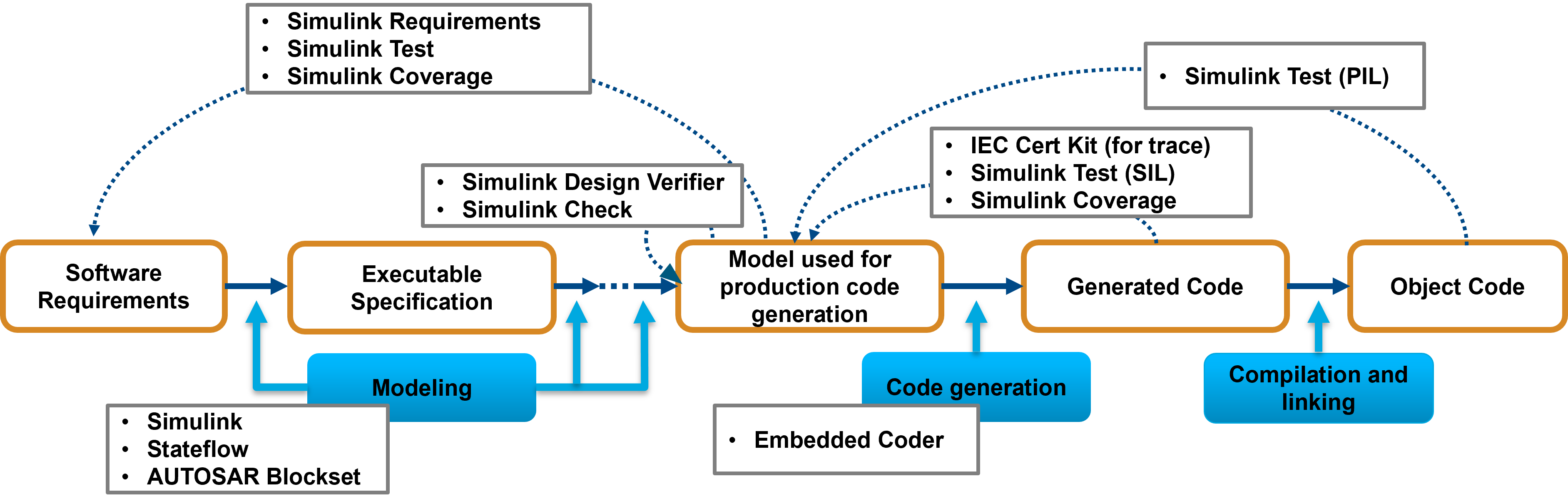

Simulink Design Verifier im Model-Based Design

Diese Abbildung veranschaulicht die Funktionen von Simulink Design Verifier in verschiedenen Phasen des Workflows für Verifikation und Validierung.

Mit Simulink Design Verifier können Sie:

versteckte Designfehler wie Ganzzahl-Überläufe oder Division-durch-Null identifizieren und Gegenbeispiele generieren, um unbeabsichtigte Funktionen zu debuggen. Sie können Modellobjekte auch für die Analyse begründen oder ausschließen.

das Modell anhand der Anforderungen mit der Requirements Toolbox™ überprüfen.

die Modellabdeckung (Simulink Coverage) erreichen, indem Sie Testfälle generieren, die die Modellabdeckungsziele erfüllen.

eine Codeabdeckungsanalyse (Embedded Coder) durchführen, indem Sie Testfälle für den von Embedded Coder® generierten Code erstellen.

bestehende Testfälle erweitern und fehlende Abdeckung erzielen.

Testfälle mit Simulink Test integrieren, um Baseline- und Äquivalenztests durchzuführen.

Industriestandards durch das IEC Certification Kit (for IEC 61508 and ISO 26262) und das DO Qualification Kit (for DO-178) erfüllen.

Simulink Design Verifier unterstützt auch die Einhaltung von Industriestandards durch das IEC Certification Kit (for IEC 61508 and ISO 26262) sowie das DO Qualification Kit (for DO-178).