HDL Neural Network Design for Digital Predistorter

This example shows how to use a neural-network-based (NN-based) digital predistorter (DPD) to compensate for the effects of nonlinearities in a power amplifier (PA). The example uses a pretrained neural network-based DPD (NN DPD). For more information on how to train the neural network, see Neural Network for Digital Predistortion Design-Offline Training example. You can generate the HDL code from this example and deploy the code onto hardware. In this example, you:

Generate orthogonal frequency-division multiplexing (OFDM) signals.

Train the NN by preprocessing the data for the DPD.

Predistort the OFDM signal with the NN DPD and send the predistorted signal through the PA.

Measure the output.

Compare the results with the memory polynomial DPD function.

Power amplifiers can cause unwanted effects in a communication system due to their nonlinear behavior. This behavior results in out-of-band emissions and in-band distortion. Digital predistortion is a baseband signal processing technique for correcting impairments in PAs. Communication systems using OFDM, such as a wireless local area network (WLAN), worldwide interoperability for microwave access (WiMax), long term evolution (LTE), and 5G new radio (NR), are vulnerable to these unwanted effects. You can apply a precorrection to the signal so that the cascade of the DPD and PA is close to an ideal, linear, and memoryless system. This linearization can improve PA power efficiency and can be more spectrum efficient. Typically, the PA nonlinear behavior is characterized in advance and DPD applies an inverse predistortion using some form of memory polynomial [ 2 ]. Experimentation with NN-based DPD techniques shows promising results that offer better performance than the traditional memory polynomial DPD [ 1 ][ 3 ][ 4 ].

Model Architecture

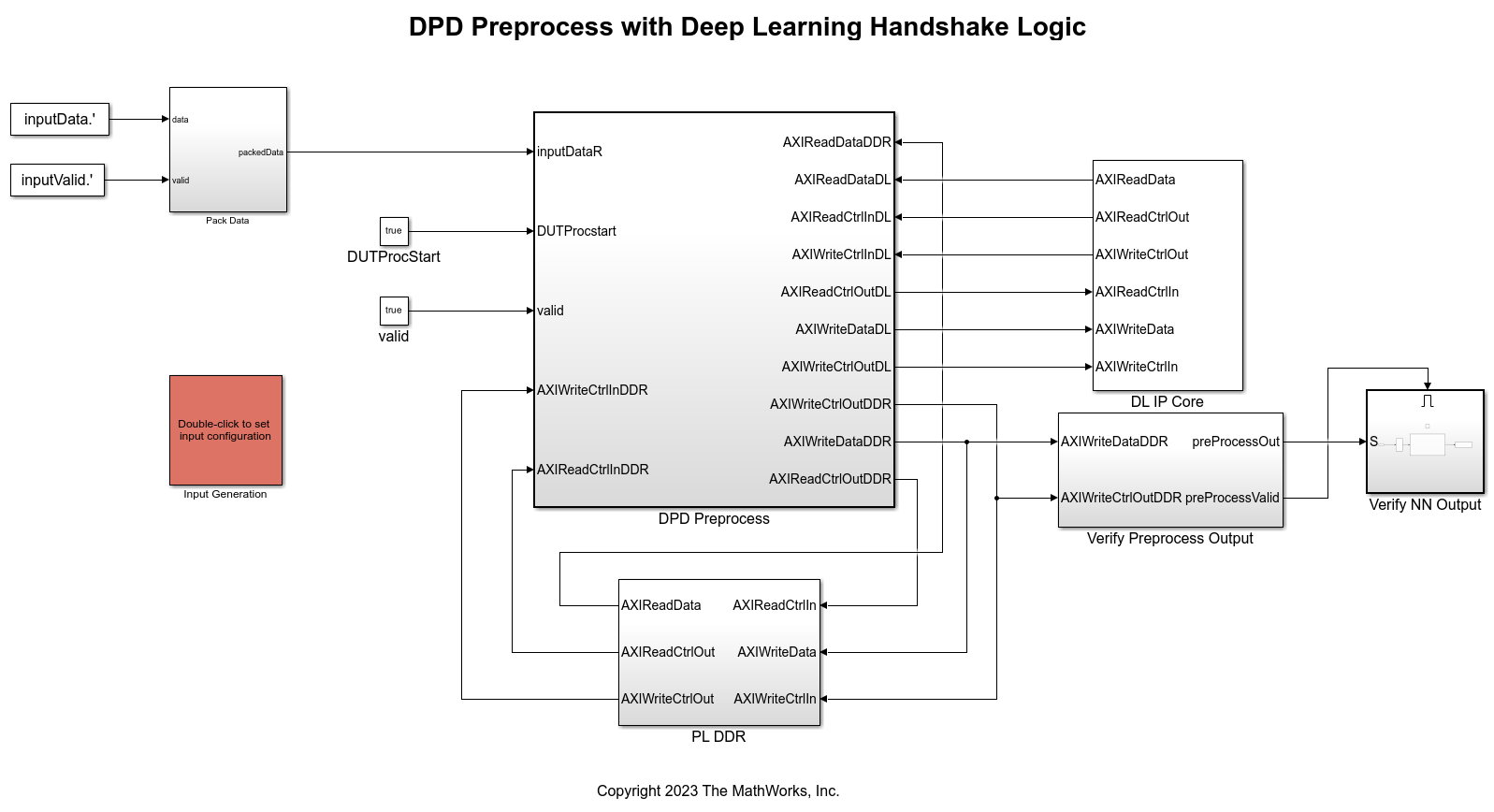

The figure shows the structure of the model in this example.

modelName = 'DPDPreprocessTestbench';

open_system(modelName);

Generate Input Data

This example uses an NXP Airfast LDMOS Doherty PA, which is connected to a local NI VST, as described in Power Amplifier Characterization. The example uses the OFDM transmitter function OFDMTx and the OFDM receiver function OFDMRx from the HDL OFDM MATLAB References example to generate and demodulate the OFDM waveform, respectively.

You can run this example with three different options based on your needs.

NI VST— Choose this option if you have NI VST and NXP PA physical devices to connect to your system.Simulated PA— Choose this option if you do not have NI VST and NXP PA physical devices and to use neural network PA model, which is trained using data captured from the PA using an NI VST..

For the NI VST and Simulation options, choose the modulation and the bandwidth from the Input Generation subsystem. To capture the effects of higher-order nonlinearities in the PA, the example oversamples the PA input by a factor of five. The Pack Data subsystem upsamples the input and packs the in-phase, quadrature-phase, and valid signal into 32-bit data and then provides the packed data as input to the DPD Preprocess subsystem.

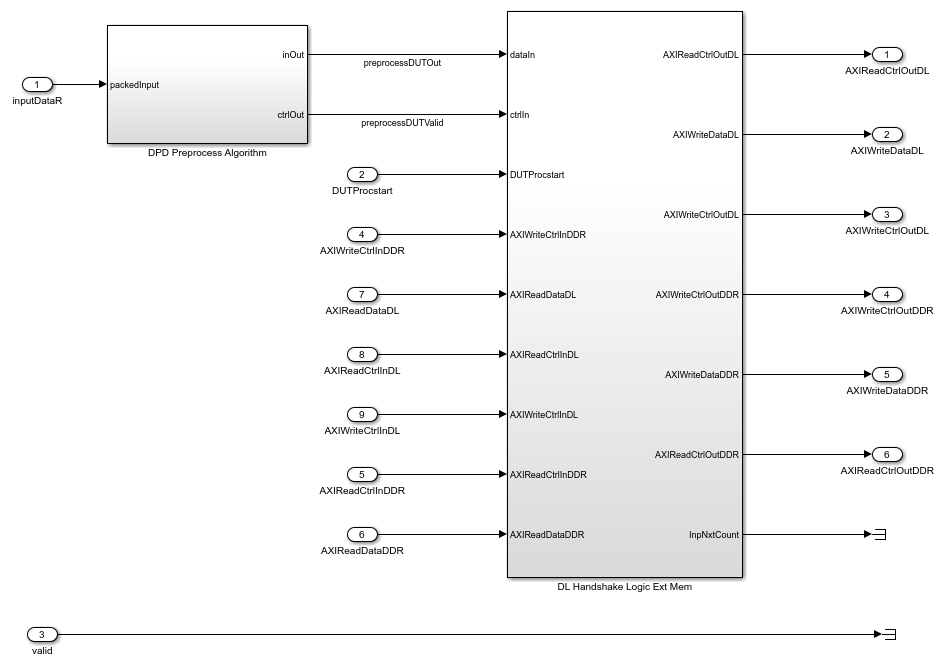

DPD Preprocess

The DPD Preprocess subsystem comprises the DPD Preprocess Algorithm and DL Handshake Logic Ext Mem blocks, as this figure shows.

load_system(modelName);

open_system([modelName '/DPD Preprocess']);

DPD Preprocess Algorithm

The DPD Preprocess Algorithm subsystem unpacks and preprocesses the input. Preprocessing involves computing the input amplitudes based on the current and previous inputs. By default, the values of the memory length and the polynomial degree are 5. Calculate the in-phase, quadrature-phase (I/Q) values, as well as five delayed versions to match the memory in the PA model. Calculate the amplitudes of the samples up to the fifth power to match the nonlinear degree of the PA model. The NN requires 30 inputs to compute the output. To calculate the output, the preprocessing algorithm must run at a higher rate than the input. So the input to the preprocess DUT must be upsampled by a factor of 36. The software then writes the preprocessed data to the DDR memory using the handshaking signals from the DL IP Core subsystem.

Handshake Algorithm

The DL Handshake Logic Ext Mem subsystem contains finite-state-machine (FSM) logic for handshaking with the DL IP Core subsystem and the PL DDR subsystem to write the frame to DDR. The Read DL Registers subsystem contains the FSM logic to read the handshaking signals, InputValid, InputAddr, and InputSize from the DL IP core. The Write to DDR subsystem uses these handshaking signals to write the preprocessed frame to the memory using the AXI stream protocol. The output write control bus from the DDR memory contains the signal wrDone, which indicates whether the frame write operation is done successful. The TriggerDLINputNext subsystem pulses the inputNext signal after the preprocessed frame is written into the DDR to indicate that the input data frame is available for processing. You can use the Verify Preprocess Output subsystem to log the signals required to verify the preprocessed data.

out = sim(modelName);

ACPR_dB NMSE_dB EVM_percent

_______ _______ ___________

No DPD -28.674 -21.287 6.8681

Memory Polynomial DPD -33.889 -27.985 2.8229

Neural Network DPD -40.552 -38.942 0.63433

Verify NN Output

The Verify NN Output subsystem sends the preprocessed data through the Predict block to collect the output from the NN. The predict (Deep Learning Toolbox) function generates responses using a trained deep neural network. The network is trained using the QPSK modulated OFDM data and the saved network is used in the predict function to generate the outputs.

The model verifies the NN DPD and comm.DPD object outputs by passing the data through the PA and computing the power spectral density (PSD), normalized mean squared error (NMSE) and adjacent channel power ratio (ACPR). The model also calculates the error vector magnitude (EVM) values by passing the outputs through the OFDM receiver and capturing the demodulated data.

You can also verify the NN output samples with the comm.DPD memory polynomial to plot the NN DPD output against the memory-polynomial-based DPD output.

Generate HDL Code

To check and generate HDL code for this example, you must have an HDL Coder™ license. Use the makehdl and makehdltb functions to generate the HDL code and testbench for the DPD Preprocess subsystem.

Synthesize the DPD Preprocess subsystem on a Xilinx® Zynq® UltraScale+(TM) MPSoC ZCU102 evaluation board. The frequency obtained after place and route is 350 MHz.

F = table(... categorical({'CLB LUT'; 'CLB Registers';'DSP';'Block RAM Tiles'}), ... categorical({'1830'; '2362'; '14';'130.5'}), ... categorical({'425280'; '850560'; '4272';'1080'}), ... categorical({'0.43'; '0.28'; '0.33';'12.08'}), ... 'VariableNames', ... {'Resources','Used','Available','Usage (%)'}); disp(F);

Resources Used Available Usage (%)

_______________ _____ _________ _________

CLB LUT 1830 425280 0.43

CLB Registers 2362 850560 0.28

DSP 14 4272 0.33

Block RAM Tiles 130.5 1080 12.08

Future Exploration

You can deploy this example to a Xilinx® Zynq® UltraScale+ MPSoC ZCU102 evaluation board. For more information, see Deploy and Verify HDL Neural Network Based DPD on FPGA (SoC Blockset) example.

References

Tarver, Chance, Liwen Jiang, Aryan Sefidi, and Joseph R. Cavallaro. "Neural Network DPD via Backpropagation through a Neural Network Model of the PA." In 2019 53rd Asilomar Conference on Signals, Systems, and Computers, 358-62. Pacific Grove, CA, USA: IEEE, 2019. https://doi.org/10.1109/IEEECONF44664.2019.9048910.

Morgan, Dennis R., Zhengxiang Ma, Jaehyeong Kim, Michael G. Zierdt, and John Pastalan. "A Generalized Memory Polynomial Model for Digital Predistortion of RF Power Amplifiers." IEEE Transactions on Signal Processing 54, no. 10 (October 2006): 3852-60. https://doi.org/10.1109/TSP.2006.879264.

Wu, Yibo, Ulf Gustavsson, Alexandre Graell i Amat, and Henk Wymeersch. "Residual Neural Networks for Digital Predistortion." In GLOBECOM 2020 - 2020 IEEE Global Communications Conference, 01-06. Taipei, Taiwan: IEEE, 2020. https://doi.org/10.1109/GLOBECOM42002.2020.9322327.

Wang, Dongming, Mohsin Aziz, Mohamed Helaoui, and Fadhel M. Ghannouchi. "Augmented Real-Valued Time-Delay Neural Network for Compensation of Distortions and Impairments in Wireless Transmitters." IEEE Transactions on Neural Networks and Learning Systems 30, no. 1 (January 2019): 242-54. https://doi.org/10.1109/TNNLS.2018.2838039.