Enable

Add enable port to subsystem or model

Libraries:

Simulink /

Ports & Subsystems

HDL Coder /

Ports & Subsystems

Description

The Enable block allows an external signal to control execution of a subsystem or a model. To enable this functionality, add the block to a Subsystem block or at the root level of a model that is referenced by a Model block.

If you use an enable port at the root-level of a model:

For multi-rate models, set the solver to single-tasking.

For models with a fixed-step size, at least one block in the model must run at the specified fixed-step size rate.

Examples

Implement Control Algorithm Using Enabled Subsystem

Use an enabled subsystems to implement a control algorithm based on a binary logic signal. The enabled subsystems execute when the binary signal has a positive value and implements the control algorithm. In this example, the super-twisting control algorithm is used to stabilize an unstable dynamic system. The super-twisting algorithm is one of the well known sliding mode control techniques for its robust performance.

Control Block States and Output of Enabled Subsystem

Reset or hold states of blocks inside an Enabled Subsystem block when the subsystem is disabled and how to control the subsystem output. In this example, you see four different combinations of state and output value configurations for both discrete and continuous control signals. When the enabled subsystem is disabled, the combinations work as follows:

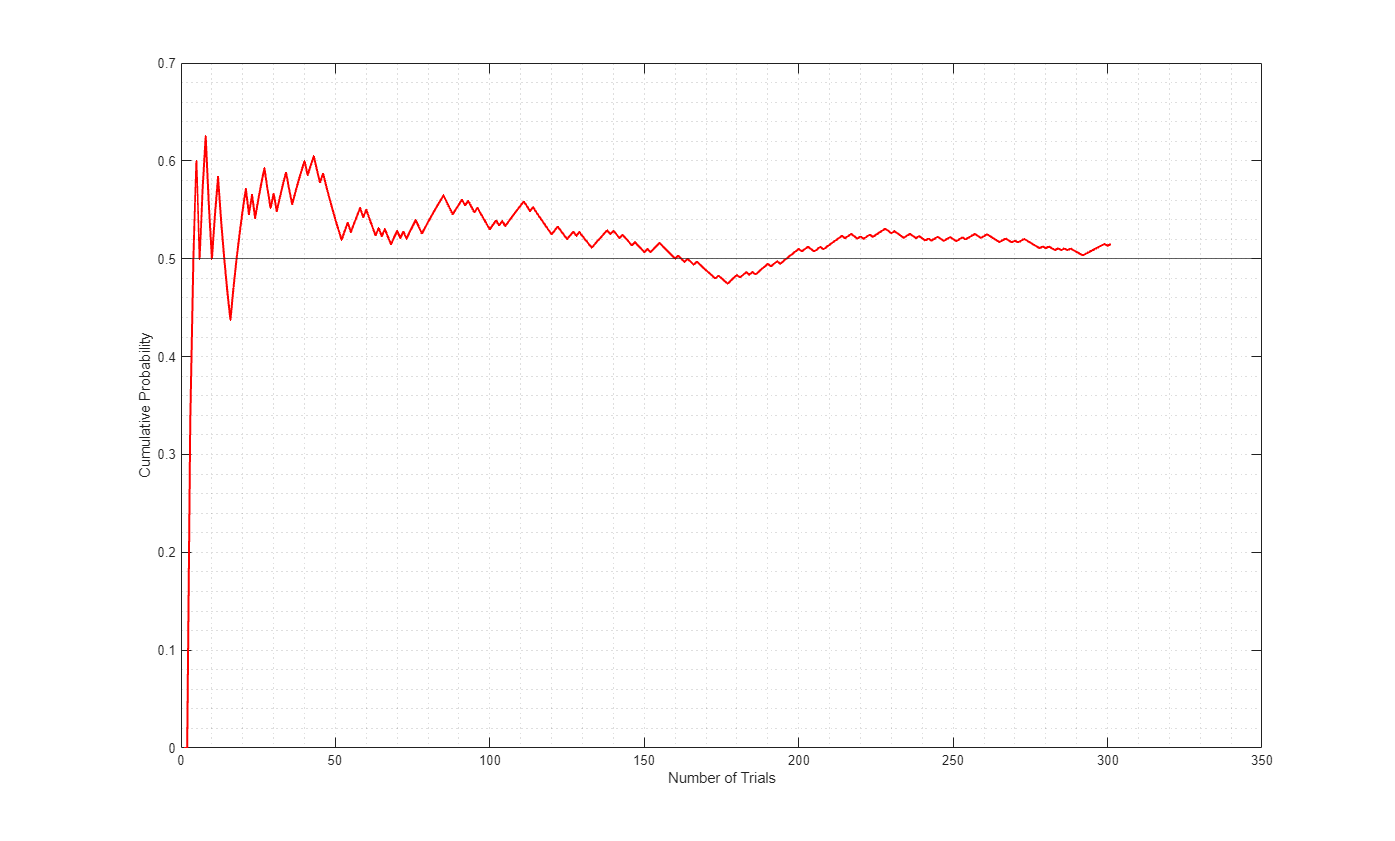

Exploring Law of Large Numbers using MATLAB System Block

Use MATLAB System blocks to illustrate the law of large numbers in Simulink.

Counters Using Conditionally Executed Subsystems

Implement counters using Enabled and Triggered subsystems. In this example, the model sldemo_counters controls flow of water into a tank and uses a counter to count the number of times overflow occurs, where overflow occurs when the water level in the tank is 8 meters or more for 30 seconds or more.

Building a Clutch Lock-Up Model

Use Simulink® to model and simulate a rotating clutch system. Although modeling a clutch system is difficult because of topological changes in the system dynamics during lockup, this example shows how enabled subsystem can easily handle such problems. We illustrate how to employ important Simulink modeling concepts in the creation of the clutch simulation. Designers can apply these concepts to many models with strong discontinuities and constraints that may change dynamically.

Ports

Output

Enable signal attached externally to the outside of an Enabled Subsystem block and passed to the inside of the subsystem. An enable signal port is added to an Enable block when you select the Show output port parameter.

Data Types: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | Boolean | fixed point | expression

Parameters

When a Subsystem block or Model block is reenabled from a disabled state, select what happens to block states for the blocks within the subsystem or model.

heldHold block states at their previous values.

resetReset block states to their initial conditions (zero if not defined).

Programmatic Use

Block parameter:

StatesWhenEnabling |

| Type: character vector |

Values:

'held' | 'reset' |

Default:

'held' |

Select when to propagate a variable-size signal.

Only when enablingPropagate a variable-size signal when reenabling a Subsystem block or Model block containing an Enable port block. When you select this option, sample time must be periodic.

During executionPropagate variable-size signals at each time step.

Programmatic Use

Block parameter:

PropagateVarSize |

| Type: character vector |

Values:

'Only when enabling' | 'During

execution' |

Default:

'Only when enabling' |

The output port passes the enable signal attached externally to the outside of an Enabled Subsystem block or enabled Model block to the inside.

- off

Remove the output port on the Enable port block.

- on

Display an output port on the Enable port block. Selecting this option allows the subsystem or model to process the enable signal.

Programmatic Use

Block parameter:

ShowOutputPort |

| Type: character vector |

Values:

'off' | 'on' |

Default:

'off' |

Control zero-crossing detection for a model.

- on

Detect zero crossings.

- off

Do not detect zero crossings.

Programmatic Use

Block parameter:

ZeroCross |

| Type: character vector |

Values:

'on' | 'off' |

Default:

'on' |

Specify dimensions for the enable signal attached externally to a Model block and passed to the inside of the block.

1Scalar signal.

[n]Vector signal of width

n.[m n]Matrix signal having

mrows andncolumns.

Programmatic Use

Block parameter:

PortDimensions |

| Type: character vector |

Values:

'1' | '[n]' | '[m

n]' |

Default:

'1' |

Specify time interval between block method execution. See Specify Sample Time.

-1Sample time inherited from the model.

TsScalar where Ts is the time interval.

[Ts, To]Vector where Ts is the time interval and To is the initial time offset.

Programmatic Use

Block parameter:

SampleTime |

| Type: character vector |

Values:

'-1' | 'Ts' | '[Ts,

To]' |

Default:

'-1' |

Specify minimum value for the enable signal attached externally to a Model block and passed to the inside of the block.

Simulink® uses this value to perform:

Simulation range checking. See Specify Signal Ranges.

Automatic scaling of fixed-point data types.

Optimization of generated code. This optimization can remove algorithmic code and affect the results of some simulation modes such as SIL or external mode. See Optimize using the specified minimum and maximum values (Embedded Coder).

[]Unspecified minimum value.

- real scalar

Real double scalar value.

Programmatic Use

Block parameter:

OutMin |

| Type: character vector |

Values:

'[]' | real scalar in quotes |

Default:

'[]' |

Specify maximum value for the enable signal attached externally to a Model block and passed to the inside of the block.

Simulink uses this value to perform:

Simulation range checking. See Specify Signal Ranges.

Automatic scaling of fixed-point data types.

Optimization of generated code. This optimization can remove algorithmic code and affect the results of some simulation modes such as SIL or external mode. See Optimize using the specified minimum and maximum values (Embedded Coder).

[]Unspecified maximum value.

- real scalar

Real double scalar value.

Programmatic Use

Block parameter:

OutMax |

| Type: character vector |

Values:

'[]' | real scalar in quotes |

Default:

'[]' |

Specify data type for the enable signal attached externally to a Model block and passed to the inside of the block.

doubleDouble-precision floating point.

singleSingle-precision floating point.

int8Signed 8-bit integer.

uint8Unsigned 8-bit integer.

int16Signed 16-bit integer.

uint16Unsigned 16-bit integer.

int32Signed 32-bit integer.

uint32Unsigned 32-bit integer.

int64Signed 64-bit integer.

uint64Unsigned 64-bit integer.

booleanBoolean with a value of

trueorfalse.fixdt(1,16)Signed 16-bit fixed point number with binary point undefined.

fixdt(1,16,0)Signed 16-bit fixed point number with binary point set to zero.

fixdt(1,16,2^,0)Signed 16-bit fixed point number with slope set to

2^0and bias set to0.<data type expression>Data type object, for example

Simulink.NumericType. You cannot enter the name of aSimulink.Busobject as a data type expression.

Programmatic Use

Block parameter:

OutDataTypeStr |

| Type: character vector |

Values:

'double' | 'single' |

'int8' | 'uint8' |

'int16' | 'uint16' |

'int32' | 'uint32' |

'int64' | 'uint64' |

'boolean' |

'<fixdt(1,16)' |

'fixdt(1,16,0)' |

'fixdt(1,16,2^0,0)' | '<data type

expression>' |

Default:

'double' |

Select data type category and display drop-down lists to help you define the data type.

Built inDisplay drop-down lists for data type and Data type override.

Fixed pointDisplay drop-down lists for Signedness, Scaling, and Data type override.

ExpressionDisplay box for entering an expression.

Dependency

To enable this parameter, select the Show data type assistant button.

Programmatic Use

No equivalent command-line parameter.

Specify value of missing workspace data when loading data from the workspace.

- on

Linearly Interpolate output at time steps for which no corresponding workspace data exists.

- off

Do not interpolate output at time steps. The current output equals the output at the most recent time step for which data exists.

Programmatic Use

Block parameter:

Interpolate |

| Type: character vector |

Values:

'on' | 'off' |

Default:

'on' |

Block Characteristics

Data Types |

|

Direct Feedthrough |

|

Multidimensional Signals |

|

Variable-Size Signals |

|

Zero-Crossing Detection |

|

Extended Capabilities

C/C++ Code Generation

Generate C and C++ code using Simulink® Coder™.

HDL Coder™ provides additional configuration options that affect HDL implementation and synthesized logic.

For more information, see HDL Code Generation in Enabled Subsystem.

This block has one default HDL architecture.

PLC Code Generation

Generate Structured Text code using Simulink® PLC Coder™.

Fixed-Point Conversion

Design and simulate fixed-point systems using Fixed-Point Designer™.

Version History

Introduced before R2006a

MATLAB Command

You clicked a link that corresponds to this MATLAB command:

Run the command by entering it in the MATLAB Command Window. Web browsers do not support MATLAB commands.

Website auswählen

Wählen Sie eine Website aus, um übersetzte Inhalte (sofern verfügbar) sowie lokale Veranstaltungen und Angebote anzuzeigen. Auf der Grundlage Ihres Standorts empfehlen wir Ihnen die folgende Auswahl: .

Sie können auch eine Website aus der folgenden Liste auswählen:

So erhalten Sie die bestmögliche Leistung auf der Website

Wählen Sie für die bestmögliche Website-Leistung die Website für China (auf Chinesisch oder Englisch). Andere landesspezifische Websites von MathWorks sind für Besuche von Ihrem Standort aus nicht optimiert.

Amerika

- América Latina (Español)

- Canada (English)

- United States (English)

Europa

- Belgium (English)

- Denmark (English)

- Deutschland (Deutsch)

- España (Español)

- Finland (English)

- France (Français)

- Ireland (English)

- Italia (Italiano)

- Luxembourg (English)

- Netherlands (English)

- Norway (English)

- Österreich (Deutsch)

- Portugal (English)

- Sweden (English)

- Switzerland

- United Kingdom (English)