LTE OFDM Modulator

Modulate LTE resource grid and return time-domain OFDM samples

Libraries:

Wireless HDL Toolbox /

Modulation

Description

The LTE OFDM Modulator block implements an algorithm for modulating LTE resource grid samples specified by LTE standard TS 36.212 [1]. The block uses an orthogonal frequency-division multiplexing (OFDM) mechanism in its operation and converts the resource grid input samples to an equivalent time-domain signal output. OFDM is effective for communication over channels with high-frequency selectivity and is widely used in the development of the LTE downlink transmitter. The block implements a windowing feature to reduce the spectral regrowth, or adjacent channel leakage ratio (ACLR), of an OFDM signal.

The block provides an interface and architecture suitable for HDL code generation and hardware deployment.

You can select the number of downlink resource blocks (NDLRB) and choose either normal or extended cyclic prefix (CP), as described in the LTE standard. The latency from the first input sample to the first output sample depends on your selection of the NDLRB.

| NDLRB | Latency |

|---|---|

| 6 | 6268 |

| 15 | 6376 |

| 25 | 6496 |

| 50 | 6796 |

| 75 | 7096 |

| 100 | 7396 |

Examples

OFDM Modulation of LTE Resource Grid Samples

Use LTE OFDM Modulator block to modulate LTE resource grid samples to equivalent time-domain signal output.

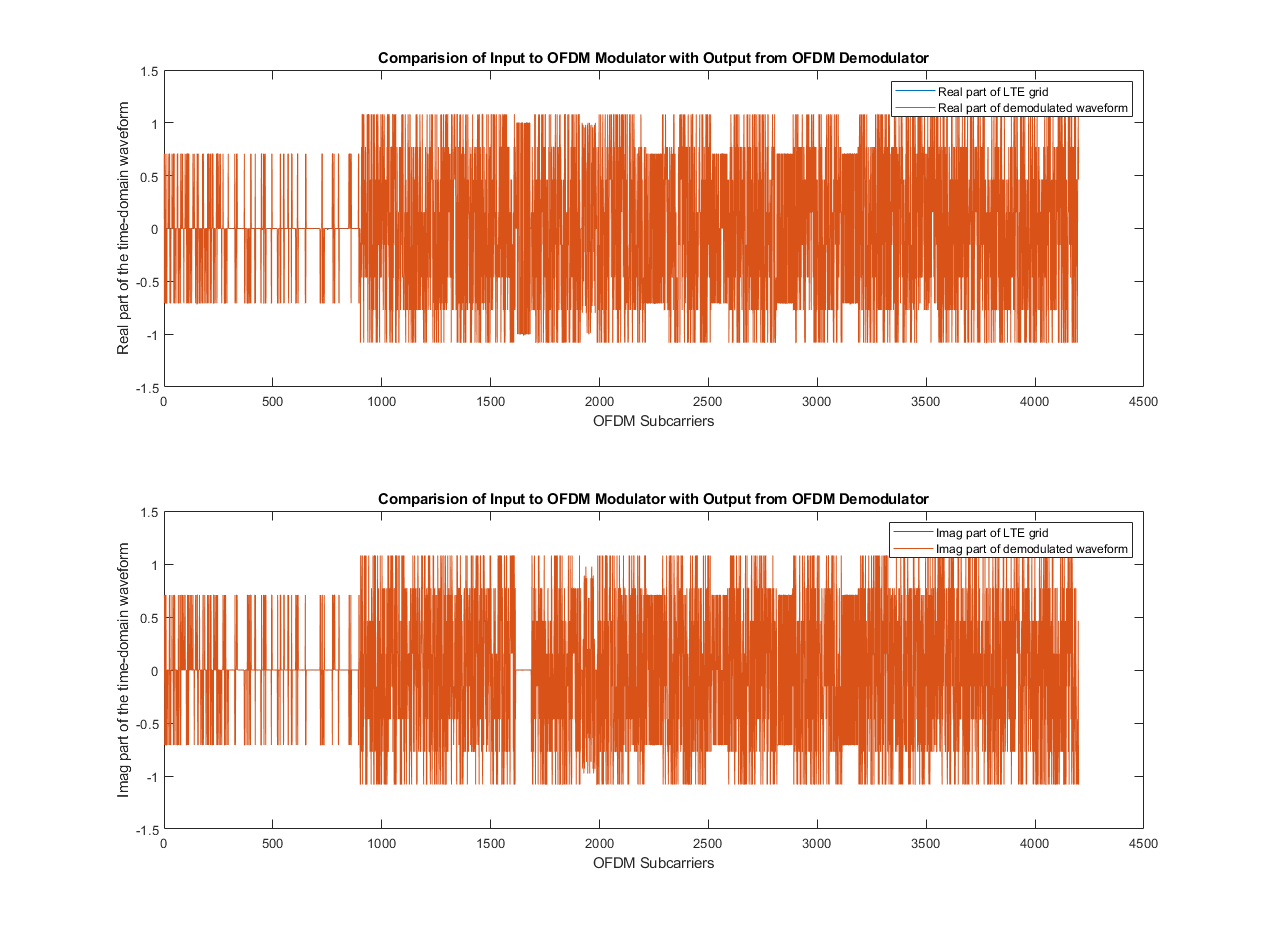

Modulate and Demodulate LTE Resource Grid

Modulate and demodulate LTE resource grid samples.

Ports

Input

Input data, specified as a signed real or complex number.

double and single data types

are supported for simulation, but not for HDL code generation.

Data Types: single | double | int8 | int16 | int32 | signed fixed point

Complex Number Support: Yes

Control signal that indicates if the data from the

data input port is valid. When this value is

1 (true), the block captures

the value on the data input port. When this value

is 0 (false), the block ignores

the values on the data input port.

Data Types: Boolean

Number of downlink resource blocks, specified as 6,

15, 25, 50,

75, or 100. The NDLRB must be

one of these six values specified by LTE standard TS 36.212 [1].

The block samples this port at the start of each subframe and ignores

any changes within a subframe.

Dependencies

To enable this port, set the NDLRB source

parameter to Input port.

Data Types: uint8 | uint16 | uint32 | fixdt(0,K,0), K >= 7 | single | double

Type of CP, specified as a Boolean scalar. When this value is

0 (false), the block selects normal CP. When this value is

1 (true), the block selects extended CP. The block samples this

port at the start of each subframe and ignores any changes within a subframe.

Dependencies

To enable this port, set the Cyclic prefix source parameter

to Input port.

Data Types: Boolean

Clears internal states, specified as a Boolean

scalar. When this value is 1

(true), the block stops the current calculation and

clears all internal states. When this value is 0

(false) and the valid input

value is 1 (true), the block

begins a new subframe.

Dependencies

To enable this port, select the Enable reset input port parameter.

Data Types: Boolean

Output

Output data, returned as a signed real or complex number. The data type is the same as the data type of the data input port. When you clear the Divide butterfly outputs by two parameter, the word length increases by 1 bit per stage in inverse fast fourier transform (IFFT).

Data Types: single | double | int8 | int16 | int32 | signed fixed point

Complex Number Support: Yes

Control signal that indicates if the data from the

data output port is valid. The block sets this

value to 1 (true) when the

modulated samples are available on the data output

port.

Data Types: Boolean

Control signal that indicates that the block is ready for new input

data. When this value is 1 (true),

the block accepts input data in the next time step. When this value is

0 (false), the block ignores

input data in the next time step.

Data Types: Boolean

Parameters

Main

You can set the NDLRB by selecting a parameter value or using an input

port. To enable the NDLRB parameter, select

Property. To enable the

NDLRB port, select Input

port.

Number of downlink resource blocks, specified as 6,

15, 25, 50,

75, or 100. NDLRB must be one

of these six values specified by LTE standard TS 36.212 [1].

Dependencies

To enable this parameter, set the NDLRB

source parameter to

Property.

You can set the cyclic prefix by selecting a parameter value or using

an input port. To enable the Cyclic prefix type

parameter, select Property. To enable the

cyclicPrefixType port, select

Input port.

Type of cyclic prefix, specified as Normal

or Extended.

Dependencies

To enable this parameter, set the Cyclic prefix

source parameter to

Property.

Select this parameter to perform a windowing operation that reduces spectral growth and uses the NDRLB window length specified by the Window length per NDLRB parameter. Clear this parameter to disable windowing operation.

NDRLB window length, specified as a row vector of nonnegative integers

whose elements correspond to the window lengths for NDRLB

6, 15, 25,

50, 75, and

100 respectively. By default, the window lengths

for NDRLB 6, 15, 25, 50, 75, and 100 are 4, 6, 4, 6, 8, and 8,

respectively. The window length for each NDLRB can range from 0 to the

minimum CP value.

For normal CP, the minimum CP values for NDRLB

6,15,25,50,75, and100are 9, 18, 36, 72, 144, and 144, respectively.For extended CP, the minimum CP values for NDRLB

6,15,25,50,75, and100are 32, 64, 128, 256, 512, and 512, respectively.

Dependencies

To enable this parameter, select the Windowing parameter.

Select this parameter to enable the reset port on the block icon.

This parameter specifies the type of sample rate for the block to select for the output data.

To provide an output data sample rate of 30.72 MHz, select

Use maximum output data sample rate.To provide an output data sample rate based on the NDLRB parameter, select

Match output data sample rate to NDLRB. The output sampling rates for NDLRB6,15,25,50,75, and100are 1.92 MHz, 3.84 MHz, 7.68 MHz, 15.36 MHz, 30.72 MHz, and 30.72 MHz, respectively.

For more information, see Base Rate Controller.

IFFT Block Parameters

When you select this parameter, the IFFT block in the LTE OFDM Modulator block implements an overall 1/N scale factor by dividing the output of each butterfly multiplication by two. This adjustment keeps the output of the IFFT block in the same amplitude range as its input. If you disable this parameter, the block avoids overflow by increasing the word length by 1 bit after each butterfly multiplication.

This parameter specifies the type of rounding mode for internal fixed-point calculations. Rounding applies to twiddle-factor multiplication and scaling operations. For more information about rounding modes, see Rounding Modes.

When the input is any integer or fixed-point data type, the IFFT

algorithm uses fixed-point arithmetic for internal calculations. This

parameter does not apply when the input data is of data type

single or double.

Algorithms

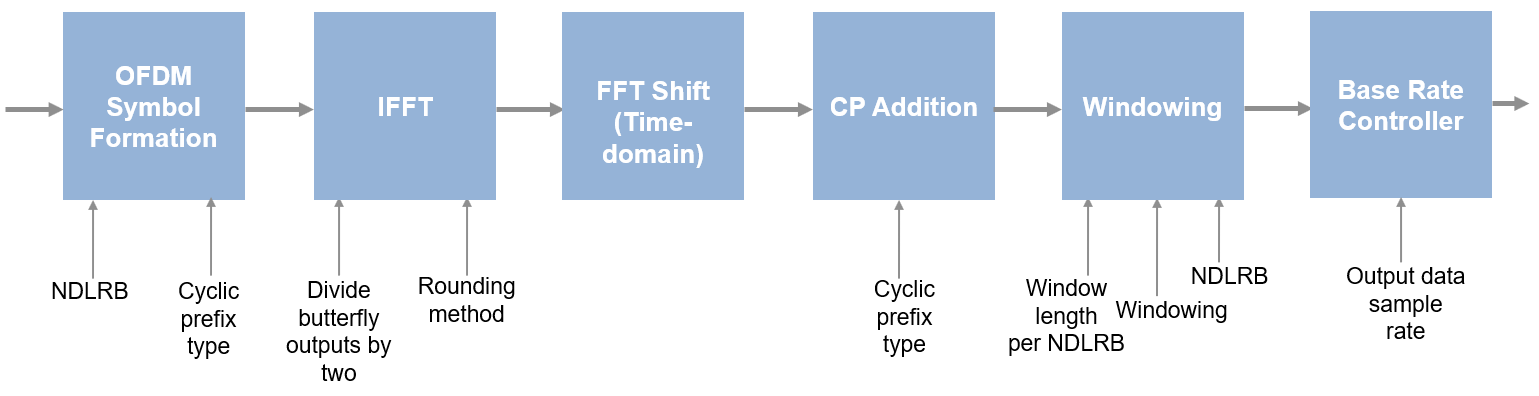

The LTE OFDM Modulator block operation sequence is carried over using these blocks: OFDM Symbol Formation, IFFT, FFT Shift, CP Addition, Windowing, and Base Rate Controller. The OFDM Symbol Formation block maps the resource grid input to active subcarrier bins to form 2048 subcarriers. The IFFT block converts the frequency-domain signal to time-domain signal, and the FFT Shift block performs time-domain FFT shift. The CP Addition block adds CP-length samples from the end of the symbol to its prefix. The Windowing block performs windowing and overlapping of adjacent OFDM symbols of complex symbols in the resource array. The Base Rate Controller block defines the sample rate of the output data. The parameters shown in the following figure configure the behavior of the block.

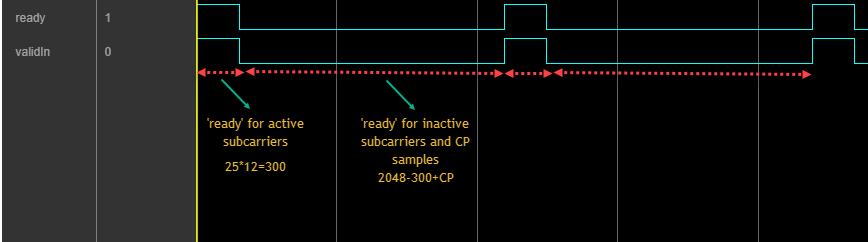

An OFDM Symbol Formation subsystem calculates the number of active and inactive subcarriers and the number of CP samples. It generates a ready signal and subcarriers (active, inactive, and DC) for each OFDM symbol as per LTE standard.

The OFDM Symbol Formation subsystem calculates the number of active subcarriers based on the NDLRB value.

Number of active subcarriers = 12 x NDLRB

The number of inactive subcarriers is a difference of IFFT size and the number of active subcarriers. To save hardware resources by avoiding multiple IFFTs, the IFFT size is fixed to 2048.

Number of inactive subcarriers = 2048 — Number of active carriers

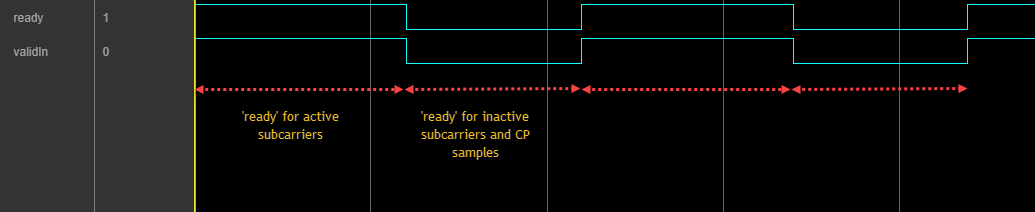

The block outputs a signal from ready port to indicate when

the block is ready to accept input data. This signal depends on the

valid input signal, NDLRB, CP type, and OFDM symbol number.

The ready output signal is generated for one time step, and the

valid input signal is checked for next time step. The block

accepts the input data and the ready output signal remains high

(1) until the OFDM symbol data is received. If the

valid input is low (0), the

ready signal extends until the valid

input signal receives high (1). After receiving active

subcarriers, the block sets the ready output signal to low

(0) for a time period equal to the sum of the number of

inactive subcarriers and the number of CP samples.

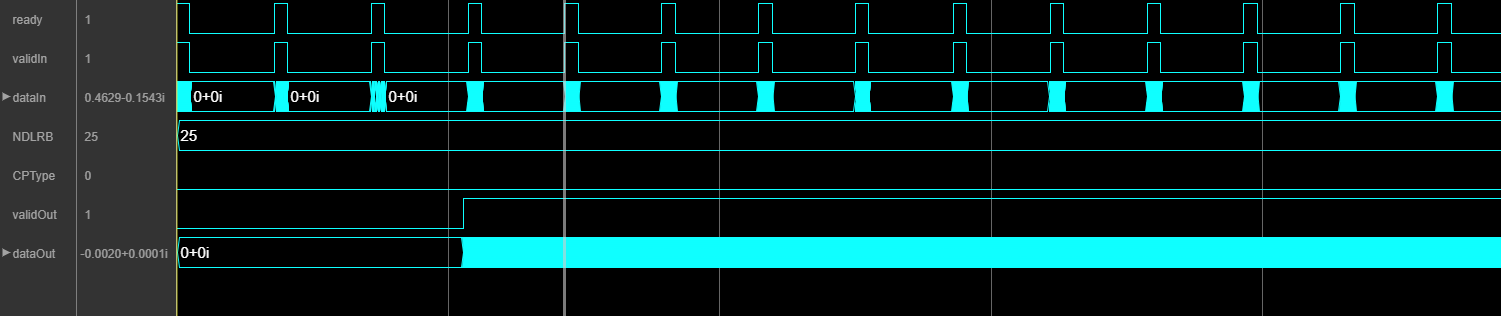

These figures show Logic Analyzer waveforms of the ready output signal for NDLRB values 25 and 100, respectively.

The IFFT block converts a frequency-domain signal to a time-domain signal. LTE supports six standard bandwidth options: 1.4 MHz, 3 MHz, 5 MHz, 10 MHz, 15 MHz, and 20 MHz. These bandwidth options require an FFT length of 128, 256, 512, 1024, and 2048, respectively. The block uses 2048 FFT length, which corresponds to the maximum bandwidth of LTE, that is 20-MHz. The FFT length of IFFT is configured to the highest FFT size to generate single hardware, which supports all LTE bandwidth options.

The Divide butterfly outputs by two parameter controls if the FFT implements an overall 1/N scale factor by dividing the output of each butterfly multiplication by two. This adjustment keeps the output of the IFFT in the same amplitude range as its input. When the Divide butterfly outputs by two parameter is cleared, the block avoids overflow by increasing the word length by 1 bit after each butterfly multiplication.

Conventionally, transceivers perform an FFT shift in the frequency domain. However, this method requires memory and introduces latency related to the size of the FFT. Instead, a transceiver can execute the same operation in the time domain using the frequency shifting property of Fourier transforms. Shifting a function in one domain corresponds to a multiplication by a complex exponential function in the other domain. To reduce hardware resources and latency, this block performs the FFT shift by multiplying the time-domain samples by a complex exponential function.

These equations describe an FFT shift. The equation for an N-point FFT is

For an FFT shift of N/2 carriers in either direction, substitute , resulting in

This equation simplifies to

Since is equivalent to , and , this equation simplifies to

The final equation shows that an FFT shift in the time domain simplifies to multiplication by (-1)n. Therefore, the block implements the FFT shift by multiplying the time-domain samples by either +1 or –1.

Cyclic prefix addition is a process of adding the last samples of an OFDM symbol as a prefix to each OFDM symbol. CP addition for an OFDM symbol with Nfft samples and CP samples NCP is shown in this figure.

The LTE OFDM Modulator block uses FFT size of 2048 for all NDLRB resources to avoid multiple IFFTs. The block uses CP values corresponding to NDLRB 100.

The Cyclic prefix type parameter controls whether the block

expects a normal or an extended CP. The block requires the input to maintain a

sample rate of 30.72 MHz. It assumes that each symbol is 2048 samples plus the

cyclic prefix size associated with the rate. When using a normal CP, the prefix of

the first symbol in each slot has 160 samples, while each subsequent symbol contains

a prefix of 144 samples. When using an extended CP, all symbols contain 512 samples.

For more information about the cyclic prefix length (in samples) of each OFDM symbol

in a subframe, see the lteOFDMModulate (LTE Toolbox) function.

Windowing reduces the spectral regrowth, or adjacent channel leakage ratio (ACLR), of an OFDM signal. The feature is optional. To enable windowing, select the Windowing parameter.

For more information about windowing, see the lteOFDMModulate (LTE Toolbox) function.

This block generates the output data at a sample rate of 30.72 MHz by using the maximum output data sample rate or output data sample rate with the specified NDLRB.

This figure shows a Logic Analyzer waveform of the output data when you set the

Output data sample rate parameter to Use

maximum output data sample rate.

This figure shows a Logic Analyzer waveform of the output data when you set the

Output data sample rate parameter to Match

output data sample rate to NDLRB parameter. For NDLRB value 25,

the output sample rate is 7.68 MHz, and the block returns valid output data at every

fourth cycle.

The performance of the synthesized HDL code varies with your target and synthesis

options. The input data type used for generating HDL code is

fixdt(1,16,14).

This table shows the resource and performance data synthesis results when using the block with default configuration. The generated HDL targeted to an AMD® Zynq® XC7Z045I-FFG900-2L FPGA. The design achieves a clock frequency of 247 MHz.

| Resource | Number Used |

|---|---|

| LUTs | 8050 |

| Registers | 9682 |

| DSPs | 22 |

| Block RAM | 22 |

| F7 Muxes | 0 |

| F8 Muxes | 0 |

| RAMB36/FIFO | 12 |

| RAMB18 | 20 |

References

[1] 3GPP TS 36.212. "Multiplexing and channel coding." 3rd Generation Partnership Project; Technical Specification Group Radio Access Network; Evolved Universal Terrestrial Radio Access (E-UTRA). URL: https://www.3gpp.org.

Extended Capabilities

This block supports C/C++ code generation for Simulink® accelerator and rapid accelerator modes and for DPI component generation.

HDL Coder™ provides additional configuration options that affect HDL implementation and synthesized logic.

This block has one default HDL architecture.

| ConstrainedOutputPipeline | Number of registers to place at

the outputs by moving existing delays within your design. Distributed

pipelining does not redistribute these registers. The default is

|

| InputPipeline | Number of input pipeline stages

to insert in the generated code. Distributed pipelining and constrained

output pipelining can move these registers. The default is

|

| OutputPipeline | Number of output pipeline stages

to insert in the generated code. Distributed pipelining and constrained

output pipelining can move these registers. The default is

|

| SynthesisAttributes |

Specifies the synthesis attributes for the blocks and block output signals in the model. The generated HDL code contains these attributes. For more information, see SynthesisAttributes (HDL Coder). |

You cannot generate HDL for this block inside a Resettable Synchronous Subsystem (HDL Coder).

Version History

Introduced in R2019a

MATLAB Command

You clicked a link that corresponds to this MATLAB command:

Run the command by entering it in the MATLAB Command Window. Web browsers do not support MATLAB commands.

Website auswählen

Wählen Sie eine Website aus, um übersetzte Inhalte (sofern verfügbar) sowie lokale Veranstaltungen und Angebote anzuzeigen. Auf der Grundlage Ihres Standorts empfehlen wir Ihnen die folgende Auswahl: .

Sie können auch eine Website aus der folgenden Liste auswählen:

So erhalten Sie die bestmögliche Leistung auf der Website

Wählen Sie für die bestmögliche Website-Leistung die Website für China (auf Chinesisch oder Englisch). Andere landesspezifische Websites von MathWorks sind für Besuche von Ihrem Standort aus nicht optimiert.

Amerika

- América Latina (Español)

- Canada (English)

- United States (English)

Europa

- Belgium (English)

- Denmark (English)

- Deutschland (Deutsch)

- España (Español)

- Finland (English)

- France (Français)

- Ireland (English)

- Italia (Italiano)

- Luxembourg (English)

- Netherlands (English)

- Norway (English)

- Österreich (Deutsch)

- Portugal (English)

- Sweden (English)

- Switzerland

- United Kingdom (English)