DVB-S2 BCH Decoder

Decode and recover message from BCH codeword according to DVB-S2 standard

Since R2022a

Libraries:

Wireless HDL Toolbox /

Error Detection and Correction

Description

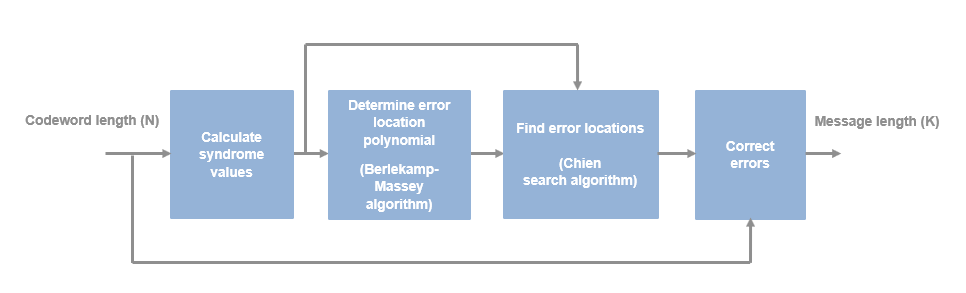

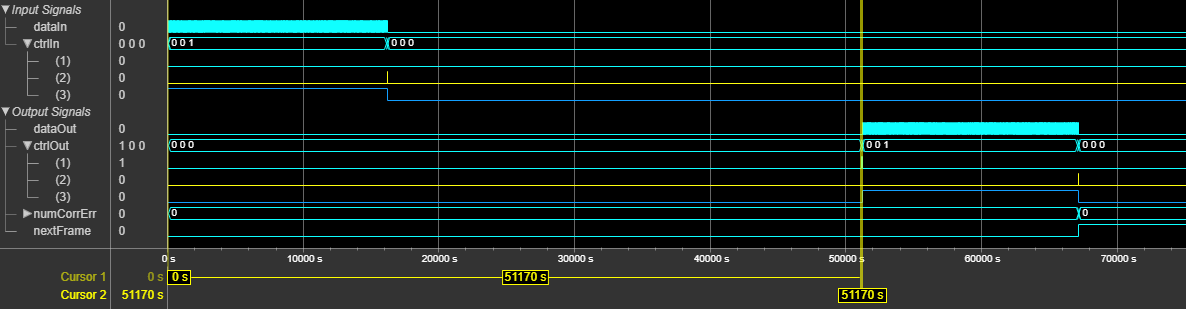

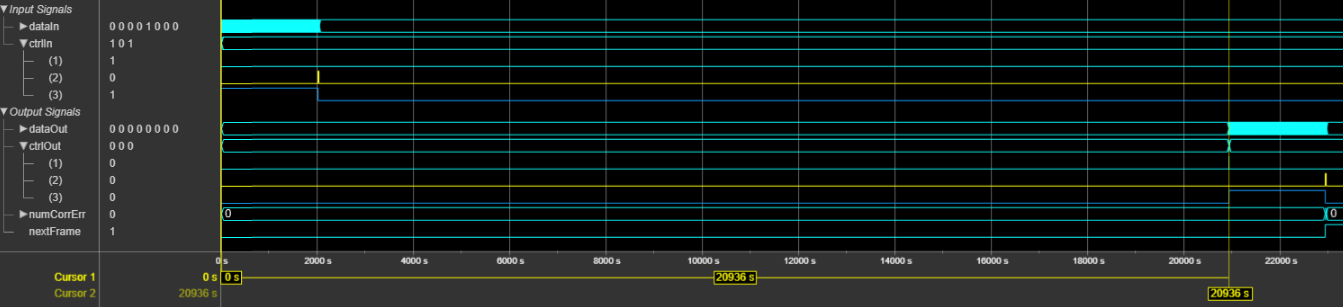

The DVB-S2 BCH Decoder block decodes and recovers messages from a Bose-Chaudhuri-Hocquenghem (BCH) codeword according to the Digital Video Broadcasting Satellite Second Generation (DVB-S2) standard [1]. The block accepts low-density parity-check (LDPC) decoded codeword data bits and a stream of control signals. It outputs decoded message data bits, a stream of control signals, a signal that indicates when the block is ready to accept new input, and an optional signal that provided the number of corrected errors in the output. The block supports either a scalar or an 8-element column vector as input.

The block supports two forward error correction (FEC) frame types, normal and short. The block provides an architecture suitable for HDL code generation and hardware deployment. You can use this block in a DVB-S2 receiver for satellite communication.

Examples

Ports

Input

Output

Parameters

Algorithms

References

[1] ETSI Standard EN 302 307 V1.4.1: Digital Video Broadcasting (DVB); Second generation framing structure, channel coding and modulation systems for Broadcasting, Interactive Services, News Gathering and other broadband satellite applications (DVB-S2), European Telecommunications Standards Institute, Valbonne, France, 2005-03.

[2] Chien, R. “Cyclic Decoding Procedures for Bose- Chaudhuri-Hocquenghem Codes.” IEEE Transactions on Information Theory 10, no. 4 (October 1964): 357–63. https://doi.org/10.1109/TIT.1964.1053699.