CCSDS RS Encoder

Libraries:

Wireless HDL Toolbox /

Error Detection and Correction

Description

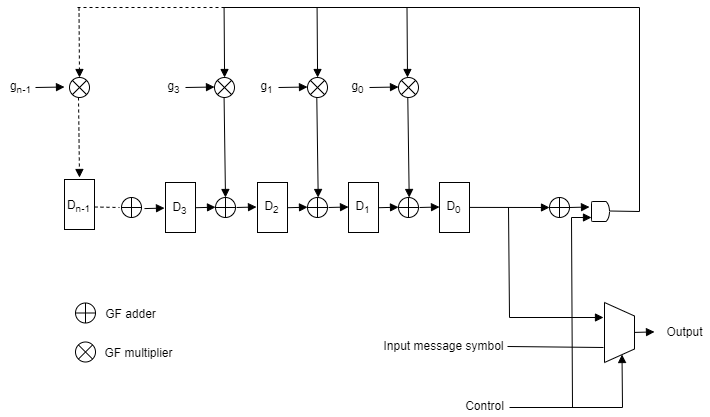

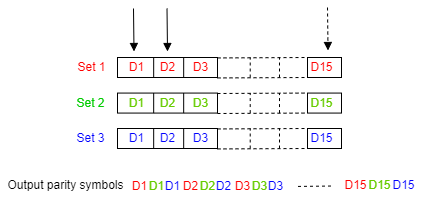

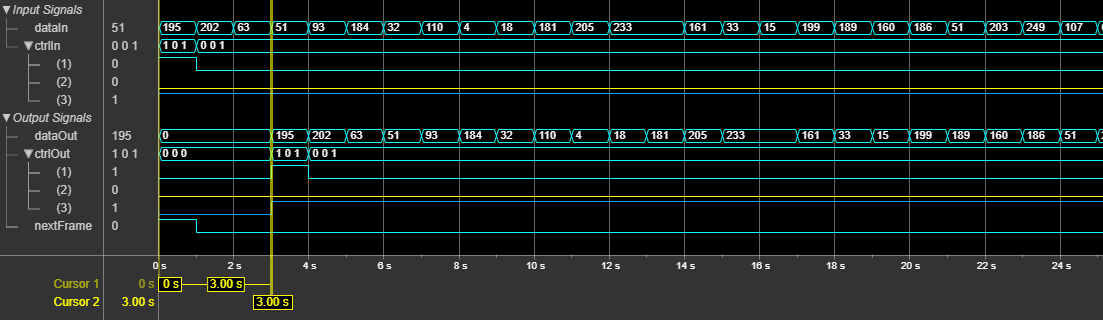

The CCSDS RS Encoder block encodes message symbols into a Reed-Solomon (RS)

codeword according to the Consultative Committee for Space Data Systems (CCSDS) standard [1]. The block accepts message

symbols and a samplecontrol bus and outputs encoded codeword data, a

samplecontrol bus, and a nextFrame signal that

indicates when the block is ready to accept new input message symbols.

The block also supports shortened message lengths. You can use this block in a CCSDS transmitter for satellite communication. The block provides an architecture suitable for HDL code generation and hardware deployment.

Examples

Ports

Input

Output

Parameters

Algorithms

References

[1] TM Synchronization and Channel Coding. Recommendation for Space Data System Standards. CCSDS 131.0-B-3. Blue Book. Issue 3. Washington, D.C.: CCSDS, September 2017.

[2] TM Synchronization and Channel Coding. Summary of Concept and Rationale CCSDS 130.1-G-3. Green Book. Issue 3, June 2020.

[3] Hsu, In-Shek , et al. "The VLSI Implementation of a Reed— Solomon Encoder Using Berlekamp’s Bit-Serial Multiplier Algorithm." IEEE Transactions on Computers, vol. C–33, no. 10 (October 1984): 906–11. https://doi.org/10.1109/TC.1984.1676351.

Extended Capabilities

Version History

Introduced in R2022a

See Also

Blocks

Functions

ccsdsRSDecode(Satellite Communications Toolbox) |ccsdsRSEncode(Satellite Communications Toolbox)