Configure Compilation, Simulation, Synthesis, and Lint Scripts

Configure the script file generation by using the EDA Tool Scripts pane. These options correspond to the properties described in Properties for Controlling Script Generation.

To view and set EDA Tool Scripts options:

Open the Configuration Parameters dialog box.

Select the HDL Code Generation > EDA Tool Scripts pane.

The Generate EDA scripts option controls the generation of script files. By default, this option is selected.

If you want to disable script generation, clear this check box and click Apply.

The list on the left of the EDA Tool Scripts pane lets you select from several categories of options. Select a category and set the options as desired. The categories are:

Compilation script: Options related to customizing scripts for compilation of generated VHDL®, Verilog® or SystemVerilog code. For more information, see Compilation Script Options.

Simulation script: Options related to customizing scripts for HDL simulators. For more information, see Simulation Script Options.

Synthesis script: Options related to customizing scripts for synthesis tools. For more information, see Synthesis Script Options.

Lint script: Options related to customizing scripts for HDL lint tools. For more information, see Lint Script Options.

Compilation Script Options

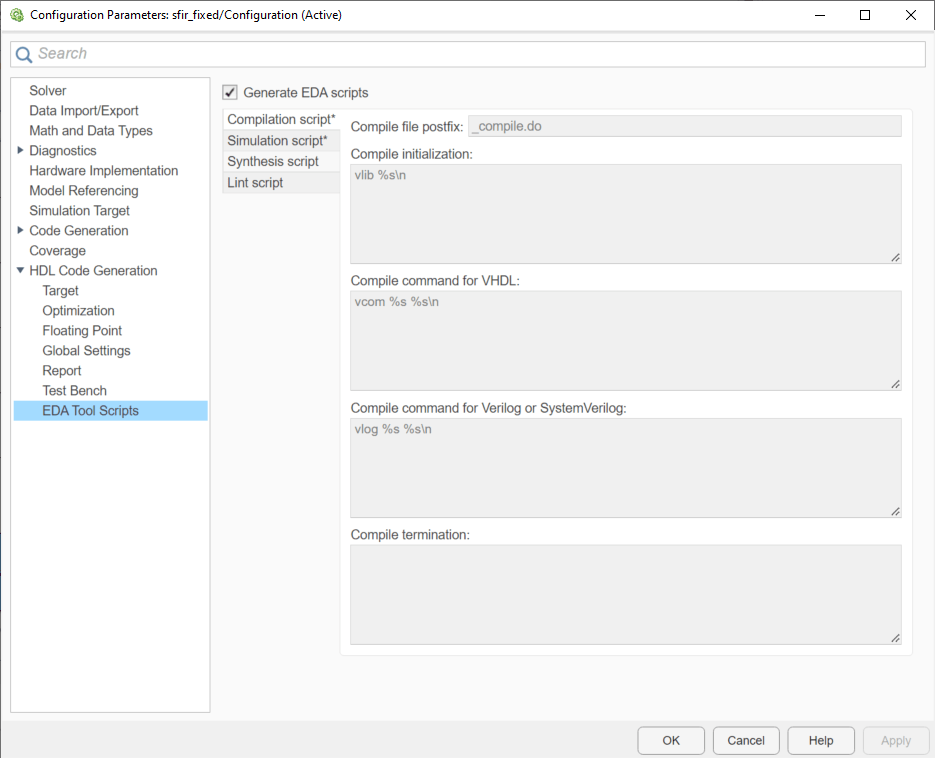

The following figure shows the Compilation script pane, with options set to their default values.

The following table summarizes the Compilation script options.

| Option and Default | Description |

|---|---|

Name: Compile file postfix Default: | Postfix appended to the DUT name or test bench name to form the script file name. |

Name: Compile initialization Default: | Format name passed to |

Name: Compile command for VHDL Default: | Format name passed to fprintf to write the Cmd

section of the compilation script for VHDL files. The two arguments are the contents of the

SimulatorFlags property option and the filename of the current entity

or module. To omit the flags, set SimulatorFlags to

'' (the default). |

Name: Compile command for Verilog or SystemVerilog Default: | Format name passed to fprintf to write the Cmd

section of the compilation script for Verilog or SystemVerilog files. The two arguments are the contents of the

SimulatorFlags property and the filename of the current entity or

module. To omit the flags, set SimulatorFlags to ''

(the default). |

Name: Compile termination Default: | Format name passed to fprintf to write the termination portion of

the compilation script. |

Simulation Script Options

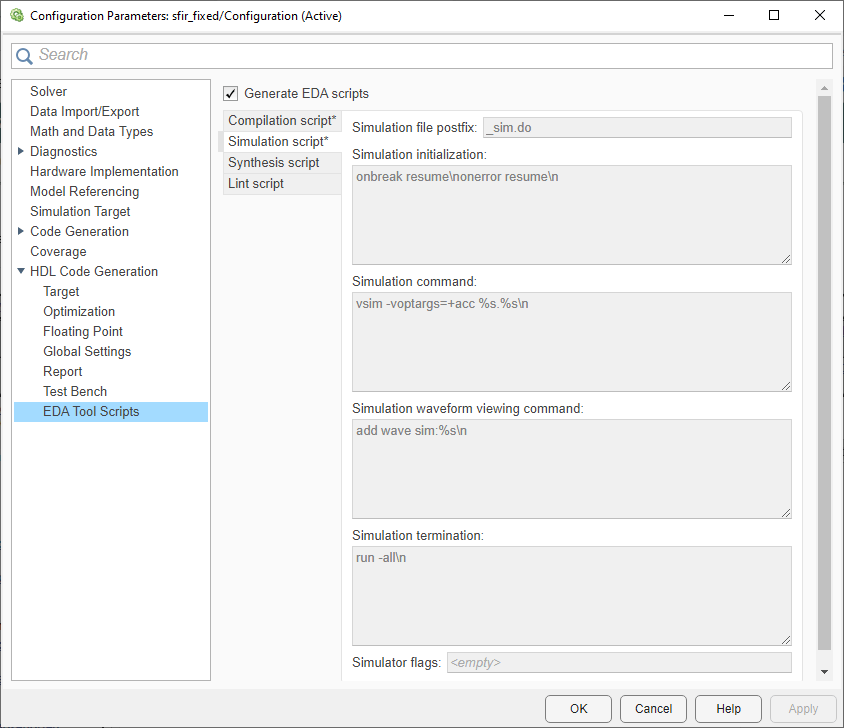

The following figure shows the Simulation script pane, with options set to their default values.

The following table summarizes the Simulation script options.

| Option and Default | Description |

|---|---|

Name: Simulation file postfix Default: | Postfix appended to the model name or test bench name to form the simulation script file name. |

Default: | Format name passed to fprintf to write the initialization section

of the simulation script. |

Default: | Format name passed to If your The second implicit argument is the top-level module or entity name. |

Simulation waveform viewing command Default: | Format name passed to fprintf to write the simulation script

waveform viewing command. The top-level module or entity signal names are implicit

arguments. |

Default: | Format name passed to fprintf to write the

Term portion of the simulation script. |

Default: | Specify options that are specific to your application and the simulator you are

using. For example, if you use the 1076-1993 VHDL compiler, specify the flag

|

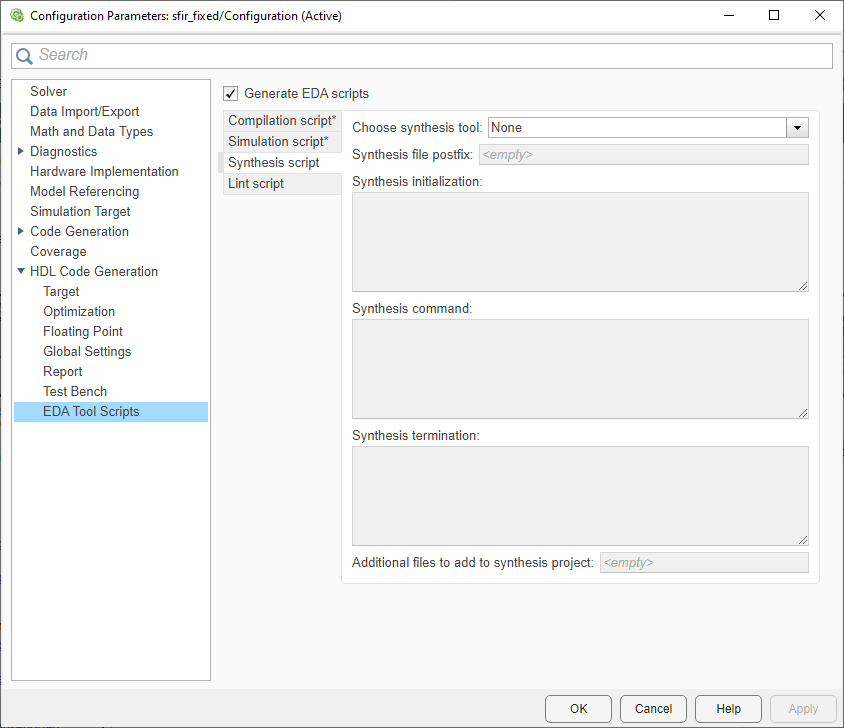

Synthesis Script Options

The following figure shows the Synthesis script pane, with options set

to their default values. The Choose synthesis tool property defaults to

None, which disables generation of a

synthesis script.

To enable synthesis script generation, select a synthesis tool from the Choose synthesis tool menu.

When you select a synthesis tool, HDL Coder™:

Enables synthesis script generation.

Enters a file name postfix (specific to the chosen synthesis tool) into the Synthesis file postfix field.

Enters strings (specific to the chosen synthesis tool) into the initialization, command, and termination fields.

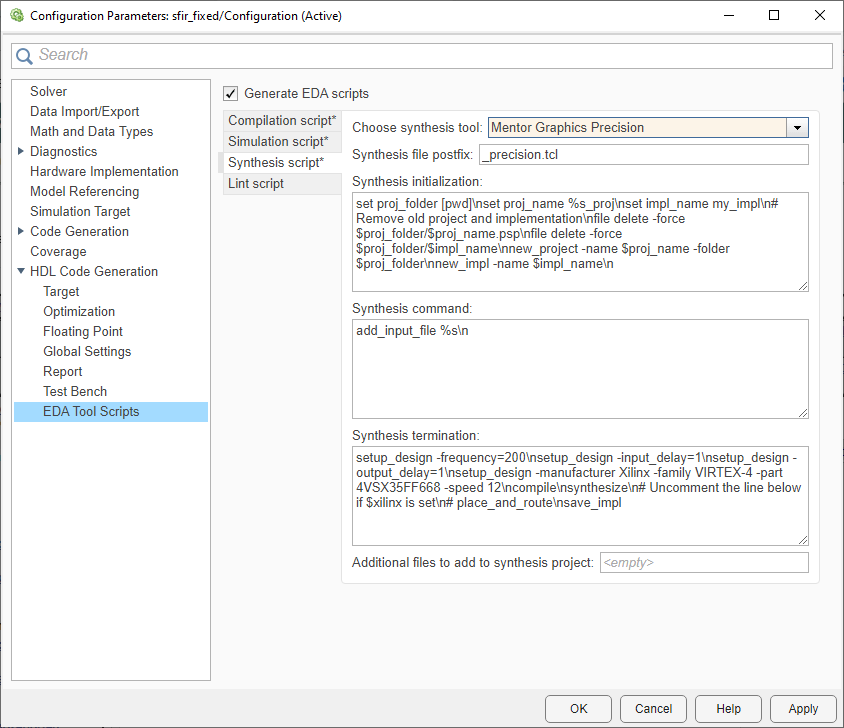

The following figure shows the default option values entered for the Mentor Graphics® Precision tool.

The following table summarizes the Synthesis script options.

| Option Name | Description | ||||||||

|---|---|---|---|---|---|---|---|---|---|

| |||||||||

Your choice of synthesis tool sets the postfix for generated synthesis file names to one of the following:

| |||||||||

Format name passed to The content of the string is specific to the selected synthesis tool. | |||||||||

Format name passed to The content of the string is specific to the selected synthesis tool. | |||||||||

Format name passed to The content of the string is specific to the selected synthesis tool. |

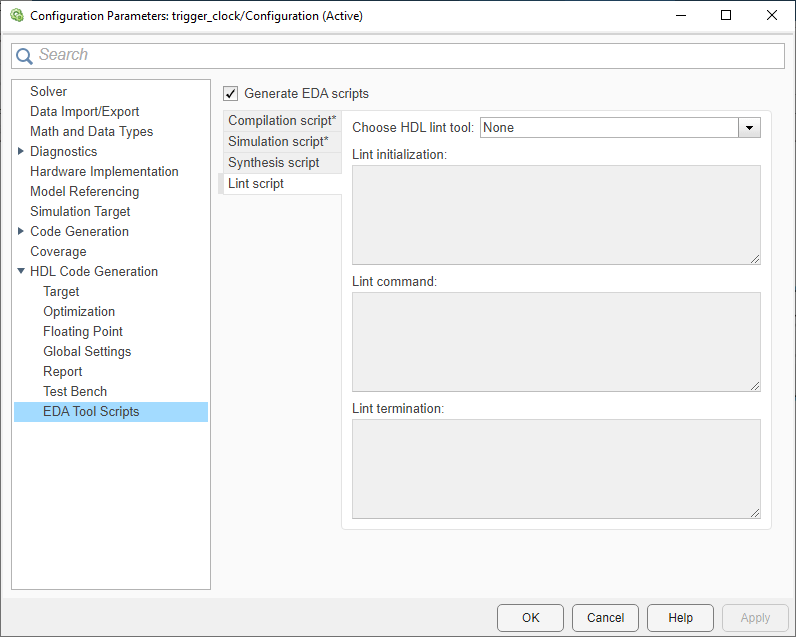

Lint Script Options

The following figure shows the Lint script pane, with options set to their default values.

The following table summarizes the Lint script options.

| Option | Description |

|---|---|

| Enable or disable generation of an HDL lint script, and select the HDL lint tool for which HDL Coder generates a script. | |

| Enter an initialization text for your HDL lint script. | |

| Enter the command for your HDL lint script. | |

| Enter a termination character vector for your HDL lint script. |

To enable lint script generation, select a HDL lint tool from the Choose HDL lint tool menu.

When you select the HDL lint tool, HDL Coder:

Enables lint script generation.

Enters strings (specific to the chosen HDL lint tool) into the initialization, command, and termination fields.

You can also generate the custom lint script. Select Custom from

the Choose HDL lint tool and enter strings into the initialization,

command, and termination fields.

For more information, see Generate HDL Lint Tool Script.