Hauptinhalt

Results for

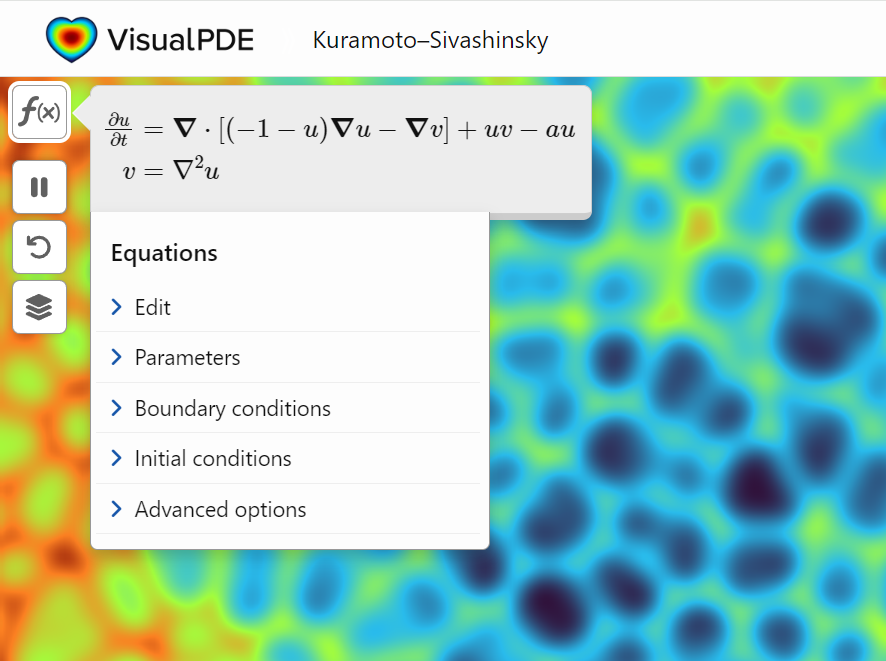

A library of runnable PDEs. See the equations! Modify the parameters! Visualize the resulting system in your browser! Convenient, fast, and instructive.

Swimming, diving

16%

Other water-based sport

4%

Gymnastics

20%

Other indoor arena sport

15%

track, field

24%

Other outdoor sport

21%

346 Stimmen

Hello, MATLAB enthusiasts! 🌟

Over the past few weeks, our community has been buzzing with insightful questions, vibrant discussions, and innovative ideas. Whether you're a seasoned expert or a curious beginner, there's something here for everyone to learn and enjoy. Let's take a moment to highlight some of the standout contributions that have sparked interest and inspired many. Dive in and see how you can join the conversation or find solutions to your own challenges!

Interesting Questions

How can i edit my code which works on r2014b version at work but not on my personal r2024a version? by Oluwadamilola Oke

Oluwadamilola Oke is seeking assistance with a MATLAB code that works on version r2014b but encounters errors on version r2024a. The issue seems to be related to file location or the use of specific commands like movefile. If you have experience with these versions of MATLAB, your expertise could be invaluable.

Yohay has been working on a simulation to measure particle speed and fit it to the Maxwell-Boltzmann distribution. However, the fit isn't aligning perfectly with the data. Yohay has shared the code and histogram data for community members to review and provide suggestions.

Alessandro Livi is toggling between C++ for Arduino Pico and MATLAB App Designer. They suggest an enhancement where typing // for comments in MATLAB automatically converts to %. This small feature could improve the workflow for many users who switch between programming languages.

Popular Discussions

Athanasios Paraskevopoulos has started an engaging discussion on Gabriel's Horn, a shape with infinite surface area but finite volume. The conversation delves into the mathematical intricacies and integral calculations required to understand this paradoxical shape.

Honzik has brought up an interesting topic about custom fonts for MATLAB. While popular coding fonts handle characters like 0 and O well, they often fail to distinguish between different types of brackets. Honzik suggests that MathWorks could develop a custom font optimized for MATLAB syntax to reduce coding errors.

From the Blogs

Guy Rouleau addresses a common error in Simulink models: "Derivative of state '1' in block 'X/Y/Integrator' at time 0.55 is not finite." The blog post explores various tools and methods to diagnose and resolve this issue, making it a valuable read for anyone facing similar challenges.

Guest writer Gianluca Carnielli, featured by Adam Danz, shares insights on creating time-sensitive animations using MATLAB. The article covers controlling the motion of multiple animated objects, organizing data with timetables, and simplifying animations with the retime function. This is a must-read for anyone interested in scientific animations.

Feel free to check out these fascinating contributions and join the discussions! Your input and expertise can make a significant difference in our community.

hello i found the following tools helpful to write matlab programs. copilot.microsoft.com chatgpt.com/gpts gemini.google.com and ai.meta.com. thanks a lot and best wishes.

Hi everyone,

I've recently joined a forest protection team in Greece, where we use drones for various tasks. This has sparked my interest in drone programming, and I'd like to learn more about it. Can anyone recommend any beginner-friendly courses or programs that teach drone programming?

I'm particularly interested in courses that focus on practical applications and might align with the work we do in forest protection. Any suggestions or guidance would be greatly appreciated!

Thank you!

I have picked the title but don't know which direction to take it. Looking for any and all inspiration. I took the project as it sounded interesting when reading into it, but I'm a satellite novice, and my degree is in electronics.

"What are your favorite features or functionalities in MATLAB, and how have they positively impacted your projects or research? Any tips or tricks to share?

Check out the LLMs with MATLAB project on File Exchange to access Large Language Models from MATLAB.

Along with the latest support for GPT-4o mini, you can use LLMs with MATLAB to generate images, categorize data, and provide semantic analyis.

Large Language Models (LLMs) with MATLAB

Connect MATLAB to Ollama™ (for local LLMs), OpenAI® Chat Completions API (which powers ChatGPT™), and Azure® OpenAI Services

function ans = your_fcn_name(n)

n;

j=sum(1:n);

a=zeros(1,j);

for i=1:n

a(1,((sum(1:(i-1))+1)):(sum(1:(i-1))+i))=i.*ones(1,i);

end

disp

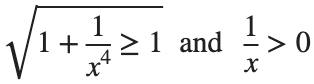

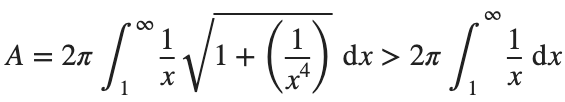

Gabriel's horn is a shape with the paradoxical property that it has infinite surface area, but a finite volume.

Gabriel’s horn is formed by taking the graph of  with the domain

with the domain  and rotating it in three dimensions about the

and rotating it in three dimensions about the  axis.

axis.

There is a standard formula for calculating the volume of this shape, for a general function  .Wwe will just state that the volume of the

.Wwe will just state that the volume of the  solid between a and b is:

solid between a and b is:

The surface area of the solid is given by:

One other thing we need to consider is that we are trying to find the value of these integrals between 1 and ∞. An integral with a limit of infinity is called an improper integral and we can't evaluate it simply by plugging the value infinity into the normal equation for a definite integral. Instead, we must first calculate the definite integral up to some finite limit b and then calculate the limit of the result as b tends to ∞:

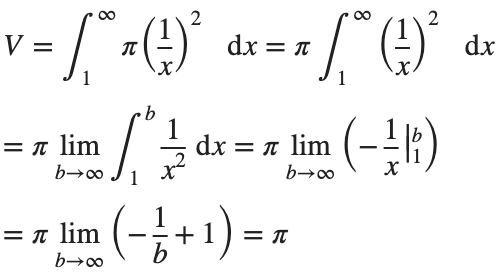

Volume

We can calculate the horn's volume using the volume integral above, so

The total volume of this infinitely long trumpet isπ.

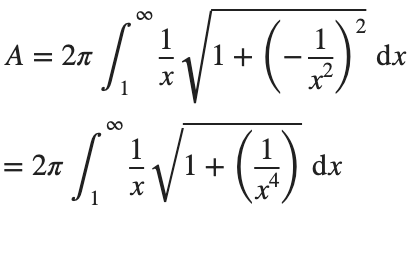

Surface Area

To determine the surface area, we first need the function’s derivative:

Now plug it into the surface area formula and we have:

This is an improper integral and it's hard to evaluate, but since in our interval

So, we have :

Now,we evaluate this last integral

So the surface are is infinite.

% Define the function for Gabriel's Horn

gabriels_horn = @(x) 1 ./ x;

% Create a range of x values

x = linspace(1, 40, 4000); % Increase the number of points for better accuracy

y = gabriels_horn(x);

% Create the meshgrid

theta = linspace(0, 2 * pi, 6000); % Increase theta points for a smoother surface

[X, T] = meshgrid(x, theta);

Y = gabriels_horn(X) .* cos(T);

Z = gabriels_horn(X) .* sin(T);

% Plot the surface of Gabriel's Horn

figure('Position', [200, 100, 1200, 900]);

surf(X, Y, Z, 'EdgeColor', 'none', 'FaceAlpha', 0.9);

hold on;

% Plot the central axis

plot3(x, zeros(size(x)), zeros(size(x)), 'r', 'LineWidth', 2);

% Set labels

xlabel('x');

ylabel('y');

zlabel('z');

% Adjust colormap and axis properties

colormap('gray');

shading interp; % Smooth shading

% Adjust the view

view(3);

axis tight;

grid on;

% Add formulas as text annotations

dim1 = [0.4 0.7 0.3 0.2];

annotation('textbox',dim1,'String',{'$$V = \pi \int_{1}^{a} \left( \frac{1}{x} \right)^2 dx = \pi \left( 1 - \frac{1}{a} \right)$$', ...

'', ... % Add an empty line for larger gap

'$$\lim_{a \to \infty} V = \lim_{a \to \infty} \pi \left( 1 - \frac{1}{a} \right) = \pi$$'}, ...

'Interpreter','latex','FontSize',12, 'EdgeColor','none', 'FitBoxToText', 'on');

dim2 = [0.4 0.5 0.3 0.2];

annotation('textbox',dim2,'String',{'$$A = 2\pi \int_{1}^{a} \frac{1}{x} \sqrt{1 + \left( -\frac{1}{x^2} \right)^2} dx > 2\pi \int_{1}^{a} \frac{dx}{x} = 2\pi \ln(a)$$', ...

'', ... % Add an empty line for larger gap

'$$\lim_{a \to \infty} A \geq \lim_{a \to \infty} 2\pi \ln(a) = \infty$$'}, ...

'Interpreter','latex','FontSize',12, 'EdgeColor','none', 'FitBoxToText', 'on');

% Add Gabriel's Horn label

dim3 = [0.3 0.9 0.3 0.1];

annotation('textbox',dim3,'String','Gabriel''s Horn', ...

'Interpreter','latex','FontSize',14, 'EdgeColor','none', 'HorizontalAlignment', 'center');

hold off

daspect([3.5 1 1]) % daspect([x y z])

view(-27, 15)

lightangle(-50,0)

lighting('gouraud')

The properties of this figure were first studied by Italian physicist and mathematician Evangelista Torricelli in the 17th century.

Acknowledgment

I would like to express my sincere gratitude to all those who have supported and inspired me throughout this project.

First and foremost, I would like to thank the mathematician and my esteemed colleague, Stavros Tsalapatis, for inspiring me with the fascinating subject of Gabriel's Horn.

I am also deeply thankful to Mr. @Star Strider for his invaluable assistance in completing the final code.

References:

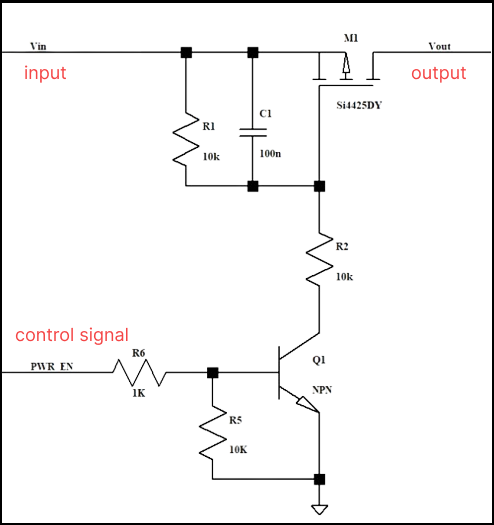

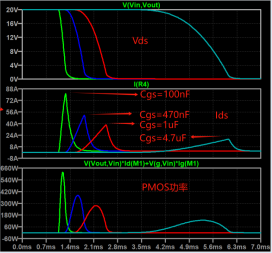

When it comes to MOS tube burnout, it is usually because it is not working in the SOA workspace, and there is also a case where the MOS tube is overcurrent.

For example, the maximum allowable current of the PMOS transistor in this circuit is 50A, and the maximum current reaches 80+ at the moment when the MOS transistor is turned on, then the current is very large.

At this time, the PMOS is over-specified, and we can see on the SOA curve that it is not working in the SOA range, which will cause the PMOS to be damaged.

So what if you choose a higher current PMOS? Of course you can, but the cost will be higher.

We can choose to adjust the peripheral resistance or capacitor to make the PMOS turn on more slowly, so that the current can be lowered.

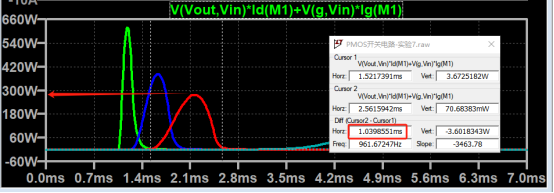

For example, when adjusting R1, R2, and the jumper capacitance between gs, when Cgs is adjusted to 1uF, The Ids are only 40A max, which is fine in terms of current, and meets the 80% derating.

(50 amps * 0.8 = 40 amps).

Next, let’s look at the power, from the SOA curve, the opening time of the MOS tube is about 1ms, and the maximum power at this time is 280W.

The normal thermal resistance of the chip is 50°C/W, and the maximum junction temperature can be 302°F.

Assuming the ambient temperature is 77°F, then the instantaneous power that 1ms can withstand is about 357W.

The actual power of PMOS here is 280W, which does not exceed the limit, which means that it works normally in the SOA area.

Therefore, when the current impact of the MOS transistor is large at the moment of turning, the Cgs capacitance can be adjusted appropriately to make the PMOS Working in the SOA area, you can avoid the problem of MOS corruption.

I am trying to earn my Intro to MATLAB badge in Cody, but I cannot click the Roll the Dice! problem. It simply is not letting me click it, therefore I cannot earn my badge. Does anyone know who I should contact or what to do?

Hello everyone, i hope you all are in good health. i need to ask you about the help about where i should start to get indulge in matlab. I am an electrical engineer but having experience of construction field. I am new here. Please do help me. I shall be waiting forward to hear from you. I shall be grateful to you. Need recommendations and suggestions from experienced members. Thank you.

I recently wrote up a document which addresses the solution of ordinary and partial differential equations in Matlab (with some Python examples thrown in for those who are interested). For ODEs, both initial and boundary value problems are addressed. For PDEs, it addresses parabolic and elliptic equations. The emphasis is on finite difference approaches and built-in functions are discussed when available. Theory is kept to a minimum. I also provide a discussion of strategies for checking the results, because I think many students are too quick to trust their solutions. For anyone interested, the document can be found at https://blanchard.neep.wisc.edu/SolvingDifferentialEquationsWithMatlab.pdf

Kindly link me to the Channel Modeling Group.

I read and compreheneded a paper on channel modeling "An Adaptive Geometry-Based Stochastic Model for Non-Isotropic MIMO Mobile-to-Mobile Channels" except the graphical results obtained from the MATLAB codes. I have tried to replicate the same graphs but to no avail from my codes. And I am really interested in the topic, i have even written to the authors of the paper but as usual, there is no reply from them. Kindly assist if possible.

Hi, I'm looking for sites where I can find coding & algorithms problems and their solutions. I'm doing this workshop in college and I'll need some problems to go over with the students and explain how Matlab works by solving the problems with them and then reviewing and going over different solution options. Does anyone know a website like that? I've tried looking in the Matlab Cody By Mathworks, but didn't exactly find what I'm looking for. Thanks in advance.

Hello, everyone! I’m Mark Hayworth, but you might know me better in the community as Image Analyst. I've been using MATLAB since 2006 (18 years). My background spans a rich career as a former senior scientist and inventor at The Procter & Gamble Company (HQ in Cincinnati). I hold both master’s & Ph.D. degrees in optical sciences from the College of Optical Sciences at the University of Arizona, specializing in imaging, image processing, and image analysis. I have 40+ years of military, academic, and industrial experience with image analysis programming and algorithm development. I have experience designing custom light booths and other imaging systems. I also work with color and monochrome imaging, video analysis, thermal, ultraviolet, hyperspectral, CT, MRI, radiography, profilometry, microscopy, NIR, and Raman spectroscopy, etc. on a huge variety of subjects.

I'm thrilled to participate in MATLAB Central's Ask Me Anything (AMA) session, a fantastic platform for knowledge sharing and community engagement. Following Adam Danz’s insightful AMA on staff contributors in the Answers forum, I’d like to discuss topics in the area of image analysis and processing. I invite you to ask me anything related to this field, whether you're seeking recommendations on tools, looking for tips and tricks, my background, or career development advice. Additionally, I'm more than willing to share insights from my experiences in the MATLAB Answers community, File Exchange, and my role as a member of the Community Advisory Board. If you have questions related to your specific images or your custom MATLAB code though, I'll invite you to ask those in the Answers forum. It's a more appropriate forum for those kinds of questions, plus you can get the benefit of other experts offering their solutions in addition to me.

For the coming weeks, I'll be here to engage with your questions and help shed light on any topics you're curious about.

Hello, everyone!

Over the past few weeks, our community has been buzzing with activity, showcasing the incredible depth of knowledge, creativity, and innovation that makes this forum such a vibrant place. Today, we're excited to highlight some of the noteworthy contributions that have sparked discussions, offered insights, and shared knowledge across various topics. Let's dive in!

Interesting Questions

Fatima Majeed brings us a thought-provoking mathematical challenge, delving into inequalities and the realms beyond (e^e). If you're up for a mathematical journey, this question is a must-see!

lil brain tackles a practical problem many of us have faced: efficiently segmenting a CSV file based on specific criteria. This post is not only a query but a learning opportunity for anyone dealing with similar data manipulation challenges.

Popular Discussions

Discover a simple yet effective trick for digit manipulation from goc3. This tip is especially handy for those frequenting Cody challenges or anyone interested in enhancing their number handling skills in MATLAB.

Chen Lin shares an exciting update about the 'Run Code' feature in the Discussions area, highlighting how our community can now directly execute and share code snippets within discussions. This feature marks a significant enhancement in how we interact and solve problems together.

From the Blogs

A Deep Dive into EEG Analysis for Predicting Neurological Outcomes By Tanya Kuruvilla

Connell D`Souza, alongside Team Swarthbeat, explores the cutting-edge application of EEG analysis in predicting neurological outcomes post-cardiac arrest. This blog post offers an in-depth look into the challenges and methodologies of modern medical data analysis.

Mihir Acharya discusses the pivotal role of MATLAB and Simulink in the future of robotics simulation. Through an engaging conversation with industry analyst George Chowdhury, this post sheds light on overcoming simulation challenges and the exciting possibilities that lie ahead.

We encourage everyone to explore these contributions further and engage with the authors and the community. Your participation is what fuels this community's continual growth and innovation.

Here's to many more discussions, discoveries, and breakthroughs together!

Twitch built an entire business around letting you watch over someone's shoulder while they play video games. I feel like we should be able to make at least a few videos where we get to watch over someone's shoulder while they solve Cody problems. I would pay good money for a front-row seat to watch some of my favorite solvers at work. Like, I want to know, did Alfonso Nieto-Castonon just sit down and bang out some of those answers, or did he have to think about it for a while? What was he thinking about while he solved it? What resources was he drawing on? There's nothing like watching a master craftsman at work.

I can imagine a whole category of Cody videos called "How I Solved It". I tried making one of these myself a while back, but as far as I could tell, nobody else made one.

Here's the direct link to the video: https://www.youtube.com/watch?v=hoSmO1XklAQ

I hereby challenge you to make a "How I Solved It" video and post it here. If you make one, I'll make another one.

Let’s Code! Make a Cody Video

Ever seen a