Corner Detector

Find corners using FAST or Harris algorithm

Libraries:

Vision HDL Toolbox /

Analysis & Enhancement

Description

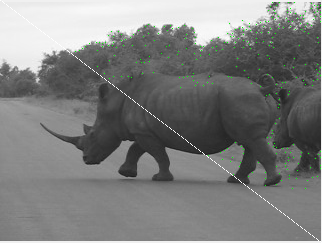

The Corner Detector block detects corners by using the features-from-accelerated-segment test (FAST) algorithm or by the intersecting edges (Harris) algorithm. For each pixel, if the pixel is a corner, the block returns the corner metric. If the pixel is not a corner, the block returns a pixel value of zero.

The FAST algorithm tests a circular area around the potential center of the corner. The test detects a corner if a contiguous section of pixels are either brighter than the center plus a threshold or darker than the center minus a threshold. You can specify a minimum contrast threshold as a parameter or port and select from three rules to define a corner. These rules specify how many pixels in a circle of pixels must exceed the minimum contrast for the center pixel to be considered a corner. The block performs parallel tests of all combinations of contiguous pixels around the circle. FAST uses very little hardware resources

The Harris algorithm computes horizontal and vertical gradients, filters the gradient components with a circular 5-by-5 Gaussian filter, and computes a metric that represents the strength of the corner. You can specify a threshold that determines the level at which corners are detected. The block returns a corner for pixels where the metric exceeds this threshold. The Harris algorithm uses more hardware resources than the FAST algorithm but can detect corners that the FAST algorithm might not find.

Examples

Ports

This block uses a streaming pixel interface with a

pixelcontrol bus for frame control signals. This interface enables the

block to operate independently of image size and format. All Vision HDL Toolbox™ blocks use the same streaming interface. The block accepts and returns a scalar

pixel value and a bus that contains five control signals. The control signals indicate the

validity of each pixel and its location in the frame. To convert a frame (pixel matrix) into a

serial pixel stream and control signals, use the Frame

To Pixels block. For a full description of the interface, see Streaming Pixel Interface.

Input

Output

Parameters

Tips

When you use a block with an internal line buffer inside an Enabled Subsystem (Simulink), the enable signal pattern must maintain the timing of the pixel stream, including the minimum blanking intervals. If the enable pattern corrupts the timing of the pixel stream, you might see partial output frames, corrupted pixel stream control signals, or mismatches between Simulink® and HDL simulation results. You may need to extend the blanking intervals to accommodate for cycles when the enable is low. For more information, see Configure Blanking Intervals.

Algorithms

References

[1] "HIGH-SPEED IMAGE FEATURE DETECTION USING FPGA IMPLEMENTATION OF FAST ALGORITHM:" Proceedings of the Third International Conference on Computer Vision Theory and Applications, SciTePress - Science and Technology Publications, 2008, pp. 174–79. doi:10.5220/0001080801740179.

[2] Rosten, E., and T. Drummond. “Fusing Points and Lines for High Performance Tracking.” Proceedings of the IEEE International Conference on Computer Vision, vol. 2, 2005, pp. 1508–11.

[3] Rosten, E., and T. Drummond. "Machine Learning for High-Speed Corner Detection." Computer Vision - ECCV 2006 Lecture Notes in Computer Science, 2006, 430-43. doi:10.1007/11744023_34.

[4] Harris, C., and M. Stephens. “A Combined Corner and Edge Detector.” In Proceedings of the Alvey Vision Conference 1988, 23.1-23.6. Manchester: Alvey Vision Club, 1988. DOI.org (Crossref), doi:10.5244/C.2.23.