Erkennen häufiger Designfehler

Bevor Sie eine Analyse zur Detektion von Designfehlern durchführen, überprüfen Sie das Modell mit dem Defect Checker auf Fehler. Der Defect Checker meldet während der gesamten Entwicklungsphase die Anzahl der Fehler in Ihrem Modell, darunter häufige und kritische Designfehler wie Division-durch-Null, Ganzzahl-Überlauf, tote Logik und Array-Out-of-Bounds.

Verwenden des Defect Checker

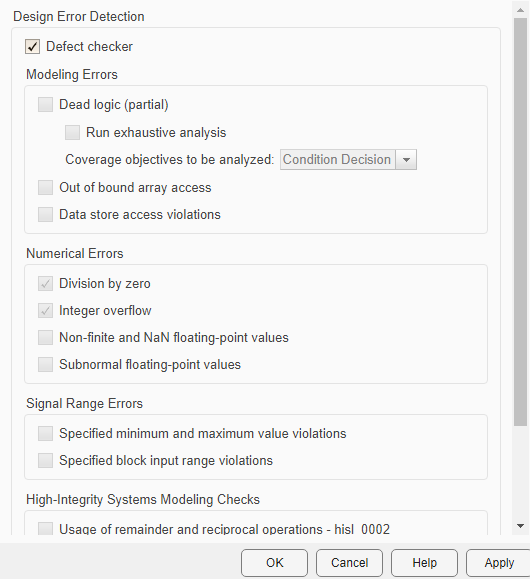

Öffnen Sie das Modell sldvexDetectDesignErrorsExample. . Überprüfen Sie auf der Registerkarte Design Verifier, ob Defect Checker ausgewählt ist.

Alternativ können Sie im Dialogfeld „Configuration Parameters“ im Fensterbereich Design Verifier > Design Error Detection überprüfen, ob Defect Checker ausgewählt ist.

Durchführen der Analyse

Um häufige Designfehler mit dem Defect Checker zu erkennen, klicken Sie auf der Registerkarte Design Verifier auf Detect Design Errors.

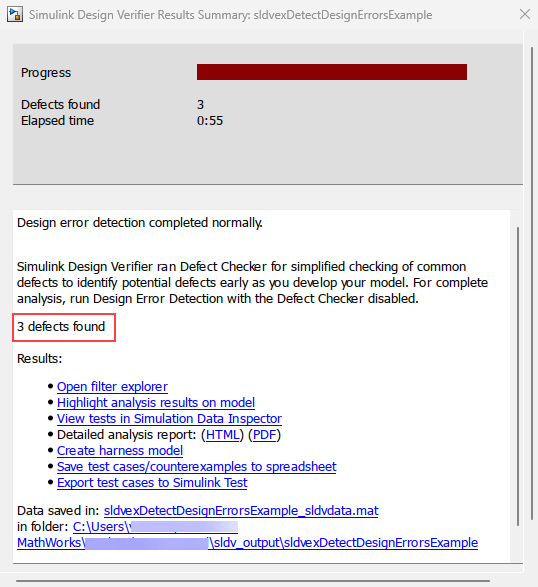

Simulink Design Verifier analysiert das Modell sldvexDetectDesignErrorsExample auf Fehler und zeigt die Anzahl der während der Analyse gefundenen Fehler im Fenster „Results Summary“ an.

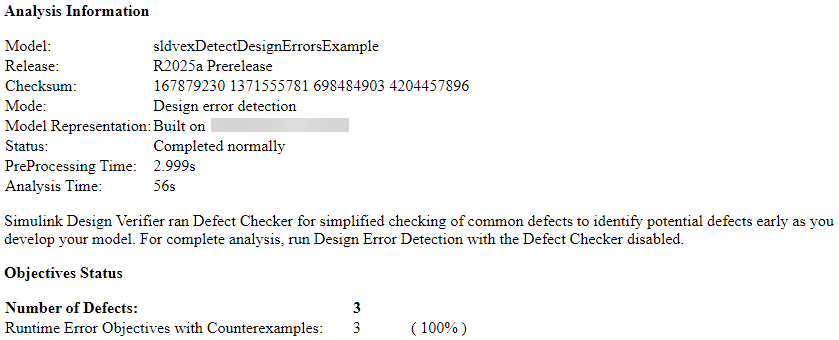

Die Analyseergebnisse zeigen, dass das Modell drei Mängel aufweist. Sie können den detaillierten Analysebericht anzeigen, indem Sie im Fenster „Results Summary“ auf HTML oder PDF klicken. Der Bericht zeigt Laufzeitfehlerziele mit den Gegenbeispielen für Sum-, Divide- und Abs-Blöcke an. Weitere Informationen zum objektiven Status finden Sie unter Review Results from Analysis Report.

Das Kapitel Analysis Information im Bericht gibt an, dass die Defect Checker-Analyse eine vereinfachte Überprüfung auf häufige Fehler durchgeführt hat.