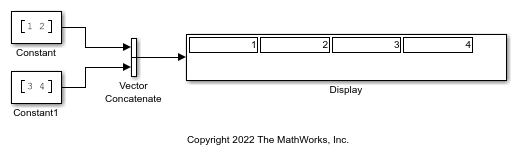

Vector Concatenate

Eingangsvektoren mit denselben Datentypen zur iterativen Verarbeitung verketten

Bibliotheken:

Simulink /

Commonly Used Blocks

Simulink /

Math Operations

Simulink /

Signal Routing

HDL Coder /

Math Operations

HDL Coder /

Signal Routing

Alternative Konfigurationen des Vector Concatenate Blocks:

Matrix Concatenate

Beschreibung

Der Vector Concatenate-Block verkettet Eingangssignale und erstellt ein nichtskalares Signal, das Sie mit einem Subsystem iterativ verarbeiten können, beispielsweise mit einem For-Each-, While-Iterator- oder For-Iterator-Subsystem.

Sie können mehrere Vector Concatenate-Blöcke verwenden, um das Ausgangssignal in mehreren Schritten zu erstellen, aber das Ergebnis ist flach, als hätten Sie einen einzelnen Block zum Verketten der Signale verwendet.

Die Signale im Ausgangssignal erscheinen in derselben Reihenfolge wie die Eingangssignale des Blocks. Eine Beschreibung der Portreihenfolge für verschiedene Blockausrichtungen finden Sie unter Identify Port Location on Rotated or Flipped Block.

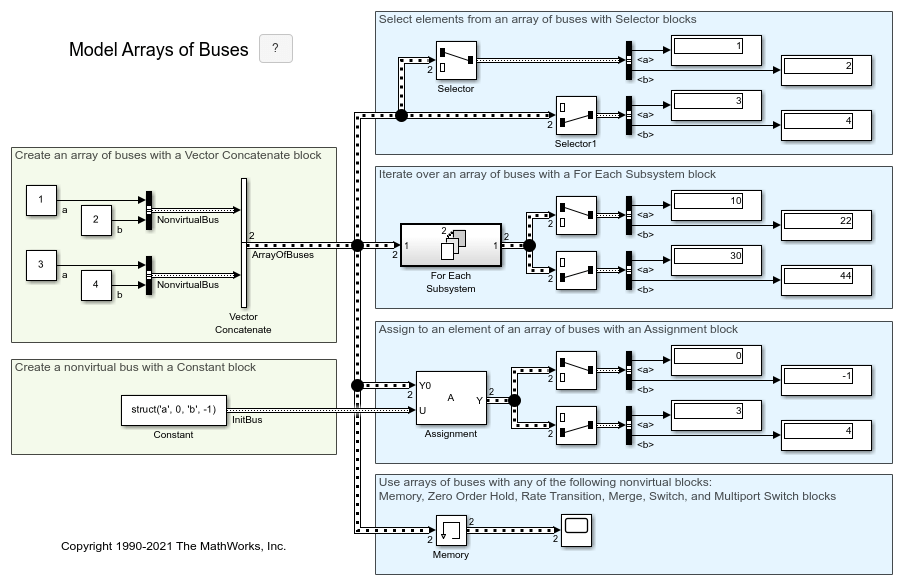

Sie müssen einen Block Vector Concatenate oder Matrix Concatenate verwenden, um ein Bus-Array zu definieren. Weitere Informationen finden Sie unter Group Nonvirtual Buses in Arrays of Buses.

Beispiele

Erweiterte Beispiele

Ports

Eingabe

Ausgabe

Parameter

Blockeigenschaften

Datentypen |

|

Direct Feedthrough |

|

Mehrdimensionale Signale |

|

Signale mit variabler Größe |

|

Erkennung von Nulldurchgängen |

|

Alternative Konfigurationen

Erweiterte Fähigkeiten

Versionsverlauf

Eingeführt in R2009b