Generate HDL Code with Record or Structure Types for Bus Signals

For a Simulink® model that contains the bus signals at the subsystem interface, you can generate code with record or structure types for those bus signals. Use the record or structure types to simplify your HDL code. The record or structure types is especially useful for simplifying interfaces and maintaining a large number of signals at the entity level.

To generate code with record or structure types for bus signals, enable the Preserve Bus structure in the generated HDL code parameter. This parameter is available in the Configuration Parameter dialog box, in the HDL Code Generation > Global Settings > Coding Style > RTL Style section.

HDL Coder™ generates record or structure types for the bus signals, an array of bus, the bus signals that have different data types, and the nested bus signals, for these interfaces:

Bus signals at design-under-test (DUT) interface

Bus signals at different subsystem-level interface

Bus signals at the model reference interface

Bus signals at black box interface

Bus signals at controlled subsystem interface

Requirements and Considerations

To generate code with record or structure types, set the target language to VHDL® or SystemVerilog. Specify the Target language option in the HDL Code Generation pane of the Configuration Parameter dialog box.

When you create a bus in your model, the

Busobject must be specified. You can create theBusobject by using the Type Editor tool. To open Type Editor, run this command in the MATLAB® Command Window:After you create atypeeditor

Busobject and specify its attributes, you can associate it with any block that needs to use the bus definition that the object provides. To associate a block with a bus, in the Block Parameters dialog box, set Output data type or Data type toBus: <object name>, replacing<object name>with theBusobject name and select the Output as nonvirtual bus. For more information, see Define Bus Properties for Reuse.When you use Preserve Bus structure in the generated HDL code option to generate record or structure for bus signal, you must turn off Scalarize ports option for your model. If Scalarize ports option is enabled, then HDL Coder does not generate record or structure types for bus signal due to the scalarization of bus ports. For more information, see Scalarize ports.

To generate record or structure types for bus signal at model reference interface, enable Generate VHDL or SystemVerilog code for model references into a single library option. For more information, see Generate VHDL or SystemVerilog code for model references into a single library.

Use Record or Structure Types for Bus in HDL Code Generation

By default, the Preserve Bus structure in the generated HDL code option is disabled. The generated code does not have record or structure types. The bus signals are flattened at the interface and are defined as individual ports in an entity in the generated code.

If your model contains the bus signals at the DUT interface or different subsystem-level interface, you can generate the HDL code with record or structure types for those bus signals.

To generate record or structure types for the bus signals in the HDL code of your DUT subsystem:

Create a

Busobject by using the Type Editor tool.Specify Output data type as the Bus object and select the Output as nonvirtual bus in the Bus Creator block. For more information, see Create Simulink Bus Objects.

Specify Target language as

VHDLorSystemVerilog.Enable the generation of record tor structure types for bus. In the configuration parameter dialog box, go to the HDL Code Generation > Global Settings > Coding Style > RTL Style section, select Preserve Bus structure in the generated HDL code.

Generate HDL code for the DUT subsystem. In the HDL Code tab, set Code for subsystem to the DUT subsystem, and then click the Generate HDL Code button.

You can also generate HDL code for your DUT with record types by setting the

GenerateRecordType argument of the makehdl function to ''on''.

makehdl(<DUT>,GenerateRecordType="on");Generate Record Types for Bus Signals at Subsystem Interface

This example shows how to generate VHDL code with record types for a model that has bus signals at the design under test (DUT) interface. The Preserve Bus structure in the generated HDL code configuration option enables you to generate code with record types for the bus signals. Use the record type to simplify your VHDL code. The record type is especially useful for simplifying interfaces and maintaining a large number of signals at the entity level.

Open Model

The Simulink® model BusSignalWithRecordTypes has a bus signal at the DUT interface. The DUT subsystem consists of a Unit Delay block. The input and output of the DUT subsystem is a bus. This bus has two bus elements with the double datatype. The Bus Creator block uses bus object BusRecordObj for creating bus signals. To load the bus object BusRecordObj, run:

run('BusRecordInput.m')

Load and open the BusSignalWithRecordTypes model by running these commands:

load_system("BusSignalWithRecordTypes"); set_param("BusSignalWithRecordTypes",'SimulationCommand','Update') open_system("BusSignalWithRecordTypes");

Generate HDL code

You can generate the HDL code for a model by using HDL Coder™. To generate HDL code for DUT subsystem with record types by setting the GenerateRecordType argument of the makehdl to "on":

makehdl("BusSignalWithRecordTypes/DUT", GenerateRecordType="on")

Generated VHDL Code for DUT Subsystem

HDL Coder defines the record type for bus signals in the VHDL package file. HDL Coder uses this package file for the port declaration of the bus signals in an entity. This code snippet shows the VHDL code of a package file that specifies record types for two bus signal. The package file defines the record BusRecordObj_record, which consists of two bus elements with the double data type.

-- --------------------------------------------------

LIBRARY IEEE;

IEEE.std_logic_1164.ALL;

USE IEEE.numeric_std.ALL; PACKAGE DUT_pkg IS

TYPE BusRecordObj_record IS RECORD

signal1 : std_logic_vector(63 DOWNTO 0);

signal2 : std_logic_vector(63 DOWNTO 0);

END RECORD BusRecordObj_record;END DUT_pkg;

These VHDL code of the DUT subsystem uses these record types for port and signals declaration of the bus signals. This code snippet shows VHDL code for a DUT subsystem which uses record types for the bus signals:

-- -------------------------------------------------------------

LIBRARY IEEE;

IEEE.std_logic_1164.ALL;

USE IEEE.numeric_std.ALL;

USE work.Subsystem_pkg.ALL; ENTITY DUT IS

PORT( clk : IN std_logic;

reset : IN std_logic;

clk_enable : IN std_logic;

In1 : IN BusRecordObj_record; -- record {double,double}

ce_out : OUT std_logic;

Out1 : OUT BusRecordObj_record -- record {double,double}

);

END DUT;ARCHITECTURE rtl OF Subsystem IS

-- Signals

SIGNAL enb : std_logic;

SIGNAL In1_signal1 : std_logic_vector(63 DOWNTO 0); -- ufix64

SIGNAL In1_signal2 : std_logic_vector(63 DOWNTO 0); -- ufix64

SIGNAL signal1 : std_logic_vector(63 DOWNTO 0); -- ufix64

SIGNAL signal2 : std_logic_vector(63 DOWNTO 0); -- ufix64

SIGNAL Unit_Delay_out1 : BusRecordObj_record; -- record {double,double}Generate Record Types for Array of Bus

This example shows model that has array of bus signal at the design under test (DUT) interface. Using Preserve Bus structure in the generated HDL code configuration option, you can generate code with array of record types for the array of bus signals.

Open Model

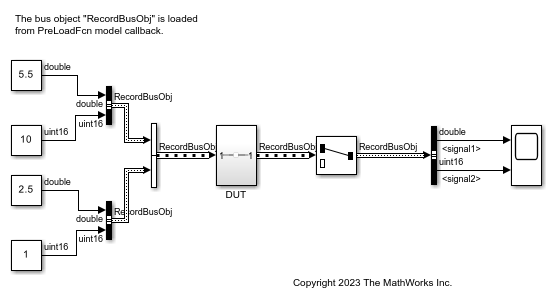

The model ArrayOfBusSignalWithRecordTypes has array of bus signal at the DUT interface. The Bus Creator block uses bus object RecordBusObj for creating bus signals. This bus object has two bus elements of datatypes, double and unit16. To load the bus object RecordBusObj, run:

run('RecordArrayOfBusInput.m')

Load and open the BusSignalWithRecordTypes model by running these commands:

load_system("ArrayOfBusSignalWithRecordTypes"); set_param("ArrayOfBusSignalWithRecordTypes",'SimulationCommand','Update') open_system("ArrayOfBusSignalWithRecordTypes");

The Vector Concatenate block generates an array of bus signal by concatenating two bus signals from the Bus Creator blocks.

Generated VHDL Code with Record Types for Array of Bus

Enable Preserve Bus structure in the generated HDL code option and generate HDL code for DUT subsystem by using this command.

makehdl("ArrayOfBusSignalWithRecordTypes/DUT",GenerateRecordType="on")

HDL Coder generates an array of record for array of bus signals in the VHDL package file. This code snippet shows the VHDL code of a package file that specifies RecordBusObj record types and vector of record for the array of bus signal.

-- -------------------------------------------------------------

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

USE IEEE.numeric_std.ALL; PACKAGE DUT_pkg IS

TYPE RecordBusObjlogicType_record IS RECORD

signal1 : std_logic_vector(63 DOWNTO 0);

signal2 : std_logic_vector(15 DOWNTO 0);

END RECORD RecordBusObjlogicType_record; TYPE vector_of_RecordBusObjlogicType_record IS ARRAY (NATURAL RANGE <>) OF BusRecordBusObjlogicType_record;

TYPE RecordBusObj_record IS RECORD

signal1 : std_logic_vector(63 DOWNTO 0);

signal2 : unsigned(15 DOWNTO 0);

END RECORD RecordBusObj_record; TYPE vector_of_RecordBusObj_record IS ARRAY (NATURAL RANGE <>) OF RecordBusObj_record;

END DUT_pkg;These VHDL code of the DUT subsystem uses these vector record for port declaration of the bus array. This code snippet shows VHDL code for a DUT subsystem which uses vector record for the bus array:

-- -------------------------------------------------------------

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

USE IEEE.numeric_std.ALL;

USE work.DUT_pkg.ALL; ENTITY DUT IS

PORT( clk : IN std_logic;

reset : IN std_logic;

clk_enable : IN std_logic;

In1 : IN vector_of_RecordBusObjlogicType_record(0 TO 1); -- record {double,uint16} [2]

ce_out : OUT std_logic;

Out1 : OUT vector_of_RecordBusObjlogicType_record(0 TO 1) -- record {double,uint16} [2]

);

END DUT;Limitations

HDL test bench generation does not support the record or structure type when you disable the Use file I/O to read/write test bench data option.

HDL test bench generation does not support the record or structure type when you enable the SystemVerilog DPI test bench option.

You cannot generate a cosimulation model for record or structure types.

Target IP core generation does not support ports with the record or structure type.

When your model contains the bus elements of complex or enumerated types, HDL Coder generates code without record or structure types for these buses.