FPGA Floating-Point Library IP Mapping

This example shows how to use vendor-specific floating-point IP libraries, such as Altera® and Xilinx®, to generate target specific HDL code. For more information on how to map designs to floating-point libraries, see Generate HDL Code for Vendor-Specific FPGA Floating-Point Target Libraries.

When you implement designs with floating-point arithmetic, you can model with higher precision and a wider dynamic range and you can avoid converting floating-point data to fixed-point data. Floating-point designs particularly beneficial for model-based design, where high-level algorithms are modeled with floating-point data and do not have implementation timing details, such as pipelining and timing constraints. However, timing details are necessary to map operations to floating-point IP modules. HDL Coder™ automatically optimizes and implements your designs with these timing details and provides interfaces for you to adjust them. HDL Coder then implements the floating-point math by integrating it with the floating-point IP modules from vendor libraries.

Open Model

This field-oriented control (FOC) algorithm example demonstrates how to map designs to floating-point libraries. For more information about this algorithm, see Field-Oriented Control of a Permanent Magnet Synchronous Machine.

This model uses single-precision data types and contains blocks that perform basic math operators, such as adders, multipliers, comparators, and complex sine and cosine functions.

This model models the signal rates at 20  or 50 KHz. This model only contains the numerical implementation, and does not have FPGA implementation timing details, such as operation latencies. All numerical operations, including the sine and cosine functions, compute in a single sample time-step.

or 50 KHz. This model only contains the numerical implementation, and does not have FPGA implementation timing details, such as operation latencies. All numerical operations, including the sine and cosine functions, compute in a single sample time-step.

load_system('hdlcoderFocCurrentSingleTargetHdl'); open_system('hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control/Sine_Cosine');

Set Up FPGA for Floating-Point Mapping

To map to a vendor-specific floating-point library, set the FPGA device by choosing a synthesis tool and chip to target. Before setting the synthesis tool, use the hdlsetuptoolpath function to set your synthesis tool path. This example uses both Altera Quartus and XILINX ISE as synthesis tools. quartuspath and isepath return synthesis tool path to the Altera Quartus II synthesis tool and the Xilinx ISE synthesis tool, respectively. For information on how to set up tools in your environment, see hdlsetuptoolpath.

hdlsetuptoolpath('ToolName', 'Altera Quartus II','ToolPath', quartuspath); hdlsetuptoolpath('ToolName', 'XILINX ISE','ToolPath', isepath);

Prepending following Altera Quartus II path(s) to the system path: D:\share\apps\HDLTools\Altera\22.1.1-mw-0\Windows\quartus\bin64 Setting XILINX environment variable to: D:\share\apps\HDLTools\Xilinx_ISE\14.7-mw-0\Win\ISE_DS\ISE Setting XILINX_EDK environment variable to: D:\share\apps\HDLTools\Xilinx_ISE\14.7-mw-0\Win\ISE_DS\EDK Setting XILINX_PLANAHEAD environment variable to: D:\share\apps\HDLTools\Xilinx_ISE\14.7-mw-0\Win\ISE_DS\PlanAhead Prepending following XILINX ISE path(s) to the system path: D:\share\apps\HDLTools\Xilinx_ISE\14.7-mw-0\Win\ISE_DS\ISE\bin\nt64;D:\share\apps\HDLTools\Xilinx_ISE\14.7-mw-0\Win\ISE_DS\ISE\lib\nt64;D:\share\apps\HDLTools\Xilinx_ISE\14.7-mw-0\Win\ISE_DS\EDK\bin\nt64;D:\share\apps\HDLTools\Xilinx_ISE\14.7-mw-0\Win\ISE_DS\EDK\lib\nt64;D:\share\apps\HDLTools\Xilinx_ISE\14.7-mw-0\Win\ISE_DS\EDK\gnuwin\bin;D:\share\apps\HDLTools\Xilinx_ISE\14.7-mw-0\Win\ISE_DS\PlanAhead\bin

Use the hdlset_param function to set the SynthesisTool and SynthesisToolChipFamily HDL model properties to Altera Quartus II and Arria 10, respectively.

hdlset_param('hdlcoderFocCurrentSingleTargetHdl', 'SynthesisTool', 'Altera Quartus II'); hdlset_param('hdlcoderFocCurrentSingleTargetHdl', 'SynthesisToolChipFamily', 'Arria 10');

Choose FPGA IP Library and Create Floating Point Configuration Object

To map to the native floating point and a vendor-specific FPGA floating point library, choose a vendor library to target. For Xilinx devices, use the XILINXLOGICORE library. For Altera devices, use the ALTERAFPFUNCTIONS or ALTFP libraries. Check the library documentation for their supported devices.

Create a floating-point target configuration object for mixed native floating-point and ALTERAFPFUNCTIONS libraries by using the createFloatingPointTargetConfig function with the VendorFloatingPointLibrary name-value argument set to ALTERAFPFUNCTIONS. For more information on creating a floating-point target configuration object, see createFloatingPointTargetConfig.

fc = hdlcoder.createFloatingPointTargetConfig(VendorFloatingPointLibrary = 'ALTERAFPFUNCTIONS')

fc =

FloatingPointTargetConfig with properties:

Library: 'NATIVEFLOATINGPOINT'

LibrarySettings: [1×1 fpconfig.NFPLatencyDrivenMode]

IPConfig: [1×1 hdlcoder.FloatingPointTargetConfig.IPConfig]

VendorLibrary: 'ALTERAFPFUNCTIONS'

VendorLibrarySettings: [1×1 fpconfig.FrequencyDrivenMode]

VendorIPConfig: [1×1 hdlcoder.FloatingPointTargetConfig.IPConfig]

Set the floating-point configuration object on the model to the configuration object fc.

hdlset_param('hdlcoderFocCurrentSingleTargetHdl', 'FloatingPointTargetConfiguration', fc);

To compile and simulate the generated code with QuestaSim, compile the Altera simulation library and set its path by using the SimulationLibPath parameter. See Set Up Tools for more information. alterasimulationlibpath returns the path to the compiled Altera simulation library.

hdlset_param('hdlcoderFocCurrentSingleTargetHdl', 'SimulationLibPath', alterasimulationlibpath);

The Altera Megafunction (ALTERAFPFUNCTIONS) library allows you to generate IP modules for a given target frequency. In this example, set the target frequency to 250MHz.

hdlset_param('hdlcoderFocCurrentSingleTargetHdl', 'TargetFrequency', 250);

Generate Code and Adjust Model for IP Mapping

Generate HDL code for the DUT subsystem, FOC_Current_Control, by using the makehdl command.

try makehdl('hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control'); catch me disp(me.message); end

### Working on the model <a href="matlab:open_system('hdlcoderFocCurrentSingleTargetHdl')">hdlcoderFocCurrentSingleTargetHdl</a>

### Generating HDL for <a href="matlab:open_system('hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control')">hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control</a>

### Using the config set for model <a href="matlab:configset.showParameterGroup('hdlcoderFocCurrentSingleTargetHdl', { 'HDL Code Generation' } )">hdlcoderFocCurrentSingleTargetHdl</a> for HDL code generation parameters.

### Running HDL checks on the model 'hdlcoderFocCurrentSingleTargetHdl'.

### Begin compilation of the model 'hdlcoderFocCurrentSingleTargetHdl'...

### Begin compilation of the model 'hdlcoderFocCurrentSingleTargetHdl'...

### Working on the model 'hdlcoderFocCurrentSingleTargetHdl'...

### Using D:\share\apps\HDLTools\Altera\22.1.1-mw-0\Windows\quartus\bin64\..\sopc_builder\bin\ip-generate for the selected floating point IP library.

### Generating Altera(R) megafunction: alterafpf_add_single for target frequency of 250 MHz.

### alterafpf_add_single takes 3 cycles.

### Done.

### Generating Altera(R) megafunction: alterafpf_mul_single for target frequency of 250 MHz.

### alterafpf_mul_single takes 3 cycles.

### Done.

### Generating Altera(R) megafunction: alterafpf_lt_single_LT for target frequency of 250 MHz.

### alterafpf_lt_single_LT takes 1 cycles.

### Done.

### Generating Altera(R) megafunction: alterafpf_gt_single_GT for target frequency of 250 MHz.

### alterafpf_gt_single_GT takes 1 cycles.

### Done.

### Generating Altera(R) megafunction: alterafpf_sub_single for target frequency of 250 MHz.

### alterafpf_sub_single takes 3 cycles.

### Done.

### Generating Altera(R) megafunction: alterafpf_neq_single_NEQ for target frequency of 250 MHz.

### alterafpf_neq_single_NEQ takes 0 cycles.

### Done.

### Generating Altera(R) megafunction: alterafpf_le_single_LE for target frequency of 250 MHz.

### alterafpf_le_single_LE takes 1 cycles.

### Done.

### Generating Altera(R) megafunction: alterafpf_ge_single_GE for target frequency of 250 MHz.

### alterafpf_ge_single_GE takes 1 cycles.

### Done.

### Delay absorption obstacles can be diagnosed by running this script: <a href="matlab:run('hdlsrc\hdlcoderFocCurrentSingleTargetHdl\highlightDelayAbsorption')">hdlsrc\hdlcoderFocCurrentSingleTargetHdl\highlightDelayAbsorption.m</a>

### To clear highlighting, click the following MATLAB script: <a href="matlab:run('hdlsrc\hdlcoderFocCurrentSingleTargetHdl\clearhighlighting.m')">hdlsrc\hdlcoderFocCurrentSingleTargetHdl\clearhighlighting.m</a>

### Creating HDL Code Generation Check Report file:///C:/Users/user/OneDrive%20-%20MathWorks/Documents/MATLAB/ExampleManager/user.Dec27/hdlcoder-ex07589604/hdlsrc/hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control_report.html

### HDL check for 'hdlcoderFocCurrentSingleTargetHdl' complete with 1 errors, 0 warnings, and 1 messages.

### HDL check for 'hdlcoderFocCurrentSingleTargetHdl' complete with 1 errors, 0 warnings, and 1 messages.

For the block 'hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control/DQ_Current_Control/Q_Current_Control'

Delay balancing unsuccessful. Cause:

The input and output configurations of this atomic subsystem cause delay balancing to fail. Consider making it non-atomic. Offending block: hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control/DQ_Current_Control/Q_Current_Control

The error messages indicate that HDL Coder cannot replace operations in feedback loops with floating-point IP modules because these loops have fewer delays than the latency of the floating-point IP modules that HDL Coder tries to replace them with. HDL Coder implements floating-point IP modules as pipelined blocks. For some modules, there are minimum latency requirements. Because changing the latency of a feedback loop generates an incorrect implementation, HDL Coder prevents the addition of latency inside these feedback loops.

The error indicates that the adder inside the feedback loop requires multiple cycles of latency budget, but the loop has only one delay.

hilite_system('hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control/DQ_Current_Control/D_Current_Control/Add');

To address these errors, you can use one of these approaches:

Reducing the target frequency may lower the pipelining depth requirement. This change may also slow down all other IP modules in the design.

Configuring the IP modules used in the loop with a smaller latency also slows down the operating frequency of the IP modules, but only for specified IP modules.

Applying clock rate pipelining. When the data rate is slower than the FPGA clock rate, the FPGA has multiple cycles at clock rate to finish operations and still retain numerical consistency. For more information about clock rate pipelining, see Clock-Rate Pipelining.

Because the sample time is 20  and the FPGA target frequency is 250 MHz, or 4 ns, you can apply clock-rate pipelining to solve the feedback loop problem by setting

and the FPGA target frequency is 250 MHz, or 4 ns, you can apply clock-rate pipelining to solve the feedback loop problem by setting TreatRatesAsHardwareRates to on. TreatRatesAsHardwarRates allows HDL Coder to determine an oversampling value automically for your design by treating your Simulink base rate as an actual hardware rate and calculating the oversampling value as the ratio between your target frequency and Simulink base rate. HDL Coder then uses the oversampling value for clock-rate pipelining. For more information, see Treat Simulink rates as actual hardware rates. For this example, the calculated oversampling value is 5000, which means that one unit delay with a sample time of 20  in the model is equivalent to 5000 clock-rate cycles at a sample time of 4 ns on the FPGA. This value is sufficient for floating-point IP modules in the loops.

in the model is equivalent to 5000 clock-rate cycles at a sample time of 4 ns on the FPGA. This value is sufficient for floating-point IP modules in the loops.

Enable TreatRatesAsHardwareRates and enable the generation of the generated and validation model.

hdlset_param('hdlcoderFocCurrentSingleTargetHdl','TreatRatesAsHardwareRates','on'); hdlset_param('hdlcoderFocCurrentSingleTargetHdl','GenerateModel','on'); hdlset_param('hdlcoderFocCurrentSingleTargetHdl','GenerateValidationModel','on');

Generate HDL code for the DUT subsystem, FOC_Current_Control, by using the makehdl command.

makehdl('hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control');

### Working on the model <a href="matlab:open_system('hdlcoderFocCurrentSingleTargetHdl')">hdlcoderFocCurrentSingleTargetHdl</a>

### Generating HDL for <a href="matlab:open_system('hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control')">hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control</a>

### Using the config set for model <a href="matlab:configset.showParameterGroup('hdlcoderFocCurrentSingleTargetHdl', { 'HDL Code Generation' } )">hdlcoderFocCurrentSingleTargetHdl</a> for HDL code generation parameters.

### Running HDL checks on the model 'hdlcoderFocCurrentSingleTargetHdl'.

### Begin compilation of the model 'hdlcoderFocCurrentSingleTargetHdl'...

### Begin compilation of the model 'hdlcoderFocCurrentSingleTargetHdl'...

### Working on the model 'hdlcoderFocCurrentSingleTargetHdl'...

### Using D:\share\apps\HDLTools\Altera\22.1.1-mw-0\Windows\quartus\bin64\..\sopc_builder\bin\ip-generate for the selected floating point IP library.

### Found an existing generated file in a previous session: (C:\Users\user\OneDrive - MathWorks\Documents\MATLAB\ExampleManager\user.Dec27\hdlcoder-ex07589604\hdlsrc\hdlcoderFocCurrentSingleTargetHdl\Altera\Arria_10\unspecified\F250\synth\alterafpf_lt_single_LT.vhd). Reusing the generated file.

### Generating Altera(R) megafunction: alterafpf_lt_single_LT for target frequency of 250 MHz.

### alterafpf_lt_single_LT takes 1 cycles.

### Done.

### Found an existing generated file in a previous session: (C:\Users\user\OneDrive - MathWorks\Documents\MATLAB\ExampleManager\user.Dec27\hdlcoder-ex07589604\hdlsrc\hdlcoderFocCurrentSingleTargetHdl\Altera\Arria_10\unspecified\F250\synth\alterafpf_gt_single_GT.vhd). Reusing the generated file.

### Generating Altera(R) megafunction: alterafpf_gt_single_GT for target frequency of 250 MHz.

### alterafpf_gt_single_GT takes 1 cycles.

### Done.

### Found an existing generated file in a previous session: (C:\Users\user\OneDrive - MathWorks\Documents\MATLAB\ExampleManager\user.Dec27\hdlcoder-ex07589604\hdlsrc\hdlcoderFocCurrentSingleTargetHdl\Altera\Arria_10\unspecified\F250\synth\alterafpf_mul_single.vhd). Reusing the generated file.

### Generating Altera(R) megafunction: alterafpf_mul_single for target frequency of 250 MHz.

### alterafpf_mul_single takes 3 cycles.

### Done.

### Found an existing generated file in a previous session: (C:\Users\user\OneDrive - MathWorks\Documents\MATLAB\ExampleManager\user.Dec27\hdlcoder-ex07589604\hdlsrc\hdlcoderFocCurrentSingleTargetHdl\Altera\Arria_10\unspecified\F250\synth\alterafpf_le_single_LE.vhd). Reusing the generated file.

### Generating Altera(R) megafunction: alterafpf_le_single_LE for target frequency of 250 MHz.

### alterafpf_le_single_LE takes 1 cycles.

### Done.

### Found an existing generated file in a previous session: (C:\Users\user\OneDrive - MathWorks\Documents\MATLAB\ExampleManager\user.Dec27\hdlcoder-ex07589604\hdlsrc\hdlcoderFocCurrentSingleTargetHdl\Altera\Arria_10\unspecified\F250\synth\alterafpf_ge_single_GE.vhd). Reusing the generated file.

### Generating Altera(R) megafunction: alterafpf_ge_single_GE for target frequency of 250 MHz.

### alterafpf_ge_single_GE takes 1 cycles.

### Done.

### Found an existing generated file in a previous session: (C:\Users\user\OneDrive - MathWorks\Documents\MATLAB\ExampleManager\user.Dec27\hdlcoder-ex07589604\hdlsrc\hdlcoderFocCurrentSingleTargetHdl\Altera\Arria_10\unspecified\F250\synth\alterafpf_sub_single.vhd). Reusing the generated file.

### Generating Altera(R) megafunction: alterafpf_sub_single for target frequency of 250 MHz.

### alterafpf_sub_single takes 3 cycles.

### Done.

### Found an existing generated file in a previous session: (C:\Users\user\OneDrive - MathWorks\Documents\MATLAB\ExampleManager\user.Dec27\hdlcoder-ex07589604\hdlsrc\hdlcoderFocCurrentSingleTargetHdl\Altera\Arria_10\unspecified\F250\synth\alterafpf_add_single.vhd). Reusing the generated file.

### Generating Altera(R) megafunction: alterafpf_add_single for target frequency of 250 MHz.

### alterafpf_add_single takes 3 cycles.

### Done.

### Found an existing generated file in a previous session: (C:\Users\user\OneDrive - MathWorks\Documents\MATLAB\ExampleManager\user.Dec27\hdlcoder-ex07589604\hdlsrc\hdlcoderFocCurrentSingleTargetHdl\Altera\Arria_10\unspecified\F250\synth\alterafpf_neq_single_NEQ.vhd). Reusing the generated file.

### Generating Altera(R) megafunction: alterafpf_neq_single_NEQ for target frequency of 250 MHz.

### alterafpf_neq_single_NEQ takes 0 cycles.

### Done.

### The code generation and optimization options you have chosen have introduced additional pipeline delays.

### The delay balancing feature has automatically inserted matching delays for compensation.

### The DUT requires an initial pipeline setup latency. Each output port experiences these additional delays.

### Output port 1: 2 cycles.

### Working on... <a href="matlab:configset.internal.open('hdlcoderFocCurrentSingleTargetHdl', 'GenerateModel')">GenerateModel</a>

### Begin model generation 'gm_hdlcoderFocCurrentSingleTargetHdl'...

### Rendering DUT with optimization related changes (IO, Area, Pipelining)...

### Model generation complete.

### Generated model saved at <a href="matlab:open_system('hdlsrc\hdlcoderFocCurrentSingleTargetHdl\gm_hdlcoderFocCurrentSingleTargetHdl.slx')">hdlsrc\hdlcoderFocCurrentSingleTargetHdl\gm_hdlcoderFocCurrentSingleTargetHdl.slx</a>

### Clock-rate pipelining obstacles can be diagnosed by running this script: <a href="matlab:run('hdlsrc\hdlcoderFocCurrentSingleTargetHdl\highlightClockRatePipelining')">hdlsrc\hdlcoderFocCurrentSingleTargetHdl\highlightClockRatePipelining.m</a>

### Delay absorption obstacles can be diagnosed by running this script: <a href="matlab:run('hdlsrc\hdlcoderFocCurrentSingleTargetHdl\highlightDelayAbsorption')">hdlsrc\hdlcoderFocCurrentSingleTargetHdl\highlightDelayAbsorption.m</a>

### To clear highlighting, click the following MATLAB script: <a href="matlab:run('hdlsrc\hdlcoderFocCurrentSingleTargetHdl\clearhighlighting.m')">hdlsrc\hdlcoderFocCurrentSingleTargetHdl\clearhighlighting.m</a>

### Generating new validation model: <a href="matlab:open_system('hdlsrc\hdlcoderFocCurrentSingleTargetHdl\gm_hdlcoderFocCurrentSingleTargetHdl_vnl')">gm_hdlcoderFocCurrentSingleTargetHdl_vnl</a>.

### Validation model generation complete.

### Begin VHDL Code Generation for 'hdlcoderFocCurrentSingleTargetHdl'.

### MESSAGE: The design requires 5000 times faster clock with respect to the base rate = 2e-05.

### Begin VHDL Code Generation for 'FOC_Current_Control_tc'.

### Working on FOC_Current_Control_tc as hdlsrc\hdlcoderFocCurrentSingleTargetHdl\FOC_Current_Control_tc.vhd.

### Code Generation for 'FOC_Current_Control_tc' completed.

### Working on... <a href="matlab:configset.internal.open('hdlcoderFocCurrentSingleTargetHdl', 'Traceability')">Traceability</a>

### Working on hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control/DQ_Current_Control/D_Current_Control/Saturate_Output/nfp_uminus_single as hdlsrc\hdlcoderFocCurrentSingleTargetHdl\nfp_uminus_single.vhd.

### Working on hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control/DQ_Current_Control/D_Current_Control/Saturate_Output as hdlsrc\hdlcoderFocCurrentSingleTargetHdl\Saturate_Output.vhd.

### Working on hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control/DQ_Current_Control/D_Current_Control as hdlsrc\hdlcoderFocCurrentSingleTargetHdl\D_Current_Control.vhd.

### Working on hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control/DQ_Current_Control as hdlsrc\hdlcoderFocCurrentSingleTargetHdl\DQ_Current_Control.vhd.

### Working on hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control/Clarke_Transform as hdlsrc\hdlcoderFocCurrentSingleTargetHdl\Clarke_Transform.vhd.

### Working on hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control/Sine_Cosine/nfp_sincos_single as hdlsrc\hdlcoderFocCurrentSingleTargetHdl\nfp_sincos_single.vhd.

### Working on hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control/Sine_Cosine as hdlsrc\hdlcoderFocCurrentSingleTargetHdl\Sine_Cosine.vhd.

### Working on hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control/Park_Transform as hdlsrc\hdlcoderFocCurrentSingleTargetHdl\Park_Transform.vhd.

### Working on hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control/Inverse_Park_Transform as hdlsrc\hdlcoderFocCurrentSingleTargetHdl\Inverse_Park_Transform.vhd.

### Working on hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control/Inverse_Clarke_Transform/nfp_gain_pow2_single as hdlsrc\hdlcoderFocCurrentSingleTargetHdl\nfp_gain_pow2_single.vhd.

### Working on hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control/Inverse_Clarke_Transform as hdlsrc\hdlcoderFocCurrentSingleTargetHdl\Inverse_Clarke_Transform.vhd.

### Working on hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control/Space_Vector_Modulation as hdlsrc\hdlcoderFocCurrentSingleTargetHdl\Space_Vector_Modulation.vhd.

### Working on hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control as hdlsrc\hdlcoderFocCurrentSingleTargetHdl\FOC_Current_Control.vhd.

### Generating package file hdlsrc\hdlcoderFocCurrentSingleTargetHdl\FOC_Current_Control_pkg.vhd.

### Code Generation for 'hdlcoderFocCurrentSingleTargetHdl' completed.

### Generating HTML files for code generation report at <a href="matlab:hdlcoder.report.openDdg('C:\Users\user\OneDrive - MathWorks\Documents\MATLAB\ExampleManager\user.Dec27\hdlcoder-ex07589604\hdlsrc\hdlcoderFocCurrentSingleTargetHdl\html\hdlcoderFocCurrentSingleTargetHdl_codegen_rpt.html')">hdlcoderFocCurrentSingleTargetHdl_codegen_rpt.html</a>

### Creating HDL Code Generation Check Report file:///C:/Users/user/OneDrive%20-%20MathWorks/Documents/MATLAB/ExampleManager/user.Dec27/hdlcoder-ex07589604/hdlsrc/hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control_report.html

### HDL check for 'hdlcoderFocCurrentSingleTargetHdl' complete with 0 errors, 0 warnings, and 5 messages.

### HDL code generation complete.

The design now maps to floating-point IP modules. The target code generation report summarizes the floating IP module usage. Open and view the generated model. For example, the subsystem gm_hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control/DQ_Current_Control/D_Current_Control/Add that corresponds to the subsystem hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control/DQ_Current_Control/D_Current_Control/Add shows that this operation takes 3 cycles.

hilite_system('gm_hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control/DQ_Current_Control/D_Current_Control/Add/Add_pd1'); get_param('gm_hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control/DQ_Current_Control/D_Current_Control/Add/Add_pd1', ... 'DelayLength')

ans =

'3'

Because floating-point IP modules introduce latencies across the design, HDL Coder adds matching delays to maintain data synchronization. See Understand Delay Balancing in HDL Coder for more details.

Share Floating-Point IPs

Floating-point IP modules are suitable to share, because they are usually identical for the same kind. Floating-point IPs are typically expensive operations and it is desirable to share these resources, if possible, to reduce the area footprint. HDL Coder shares resources in the same subsystem. In order to allow more resources to share, flatten the subsystem hierarchy and set resource sharing factor on the top network to 4.

hdlset_param('hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control', 'FlattenHierarchy', 'on'); hdlset_param('hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control', 'SharingFactor', 4);

Generate HDL code for the DUT subsystem, FOC_Current_Control, by using the makehdl command.

makehdl('hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control');

### Working on the model <a href="matlab:open_system('hdlcoderFocCurrentSingleTargetHdl')">hdlcoderFocCurrentSingleTargetHdl</a>

### Generating HDL for <a href="matlab:open_system('hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control')">hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control</a>

### Using the config set for model <a href="matlab:configset.showParameterGroup('hdlcoderFocCurrentSingleTargetHdl', { 'HDL Code Generation' } )">hdlcoderFocCurrentSingleTargetHdl</a> for HDL code generation parameters.

### Running HDL checks on the model 'hdlcoderFocCurrentSingleTargetHdl'.

### Begin compilation of the model 'hdlcoderFocCurrentSingleTargetHdl'...

### Begin compilation of the model 'hdlcoderFocCurrentSingleTargetHdl'...

### Working on the model 'hdlcoderFocCurrentSingleTargetHdl'...

### Found an existing generated file in a previous session: (C:\Users\user\OneDrive - MathWorks\Documents\MATLAB\ExampleManager\user.Dec27\hdlcoder-ex07589604\hdlsrc\hdlcoderFocCurrentSingleTargetHdl\Altera\Arria_10\unspecified\F250\synth\alterafpf_add_single.vhd). Reusing the generated file.

### Generating Altera(R) megafunction: alterafpf_add_single for target frequency of 250 MHz.

### alterafpf_add_single takes 3 cycles.

### Done.

### Found an existing generated file in a previous session: (C:\Users\user\OneDrive - MathWorks\Documents\MATLAB\ExampleManager\user.Dec27\hdlcoder-ex07589604\hdlsrc\hdlcoderFocCurrentSingleTargetHdl\Altera\Arria_10\unspecified\F250\synth\alterafpf_sub_single.vhd). Reusing the generated file.

### Generating Altera(R) megafunction: alterafpf_sub_single for target frequency of 250 MHz.

### alterafpf_sub_single takes 3 cycles.

### Done.

### Found an existing generated file in a previous session: (C:\Users\user\OneDrive - MathWorks\Documents\MATLAB\ExampleManager\user.Dec27\hdlcoder-ex07589604\hdlsrc\hdlcoderFocCurrentSingleTargetHdl\Altera\Arria_10\unspecified\F250\synth\alterafpf_mul_single.vhd). Reusing the generated file.

### Generating Altera(R) megafunction: alterafpf_mul_single for target frequency of 250 MHz.

### alterafpf_mul_single takes 3 cycles.

### Done.

### Found an existing generated file in a previous session: (C:\Users\user\OneDrive - MathWorks\Documents\MATLAB\ExampleManager\user.Dec27\hdlcoder-ex07589604\hdlsrc\hdlcoderFocCurrentSingleTargetHdl\Altera\Arria_10\unspecified\F250\synth\alterafpf_lt_single_LT.vhd). Reusing the generated file.

### Generating Altera(R) megafunction: alterafpf_lt_single_LT for target frequency of 250 MHz.

### alterafpf_lt_single_LT takes 1 cycles.

### Done.

### Found an existing generated file in a previous session: (C:\Users\user\OneDrive - MathWorks\Documents\MATLAB\ExampleManager\user.Dec27\hdlcoder-ex07589604\hdlsrc\hdlcoderFocCurrentSingleTargetHdl\Altera\Arria_10\unspecified\F250\synth\alterafpf_gt_single_GT.vhd). Reusing the generated file.

### Generating Altera(R) megafunction: alterafpf_gt_single_GT for target frequency of 250 MHz.

### alterafpf_gt_single_GT takes 1 cycles.

### Done.

### Using D:\share\apps\HDLTools\Altera\22.1.1-mw-0\Windows\quartus\bin64\..\sopc_builder\bin\ip-generate for the selected floating point IP library.

### Found an existing generated file in a previous session: (C:\Users\user\OneDrive - MathWorks\Documents\MATLAB\ExampleManager\user.Dec27\hdlcoder-ex07589604\hdlsrc\hdlcoderFocCurrentSingleTargetHdl\Altera\Arria_10\unspecified\F250\synth\alterafpf_neq_single_NEQ.vhd). Reusing the generated file.

### Generating Altera(R) megafunction: alterafpf_neq_single_NEQ for target frequency of 250 MHz.

### alterafpf_neq_single_NEQ takes 0 cycles.

### Done.

### Found an existing generated file in a previous session: (C:\Users\user\OneDrive - MathWorks\Documents\MATLAB\ExampleManager\user.Dec27\hdlcoder-ex07589604\hdlsrc\hdlcoderFocCurrentSingleTargetHdl\Altera\Arria_10\unspecified\F250\synth\alterafpf_ge_single_GE.vhd). Reusing the generated file.

### Generating Altera(R) megafunction: alterafpf_ge_single_GE for target frequency of 250 MHz.

### alterafpf_ge_single_GE takes 1 cycles.

### Done.

### Found an existing generated file in a previous session: (C:\Users\user\OneDrive - MathWorks\Documents\MATLAB\ExampleManager\user.Dec27\hdlcoder-ex07589604\hdlsrc\hdlcoderFocCurrentSingleTargetHdl\Altera\Arria_10\unspecified\F250\synth\alterafpf_le_single_LE.vhd). Reusing the generated file.

### Generating Altera(R) megafunction: alterafpf_le_single_LE for target frequency of 250 MHz.

### alterafpf_le_single_LE takes 1 cycles.

### Done.

### Working on... <a href="matlab:configset.internal.open('hdlcoderFocCurrentSingleTargetHdl', 'GenerateModel')">GenerateModel</a>

### Begin model generation 'gm_hdlcoderFocCurrentSingleTargetHdl'...

### Rendering DUT with optimization related changes (IO, Area, Pipelining)...

### Model generation complete.

### Generated model saved at <a href="matlab:open_system('hdlsrc\hdlcoderFocCurrentSingleTargetHdl\gm_hdlcoderFocCurrentSingleTargetHdl.slx')">hdlsrc\hdlcoderFocCurrentSingleTargetHdl\gm_hdlcoderFocCurrentSingleTargetHdl.slx</a>

### Generating new validation model: <a href="matlab:open_system('hdlsrc\hdlcoderFocCurrentSingleTargetHdl\gm_hdlcoderFocCurrentSingleTargetHdl_vnl')">gm_hdlcoderFocCurrentSingleTargetHdl_vnl</a>.

### Validation model generation complete.

### Begin VHDL Code Generation for 'hdlcoderFocCurrentSingleTargetHdl'.

### MESSAGE: The design requires 5000 times faster clock with respect to the base rate = 2e-05.

### Begin VHDL Code Generation for 'FOC_Current_Control_tc'.

### Working on FOC_Current_Control_tc as hdlsrc\hdlcoderFocCurrentSingleTargetHdl\FOC_Current_Control_tc.vhd.

### Code Generation for 'FOC_Current_Control_tc' completed.

### Working on... <a href="matlab:configset.internal.open('hdlcoderFocCurrentSingleTargetHdl', 'Traceability')">Traceability</a>

### Working on hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control/nfp_gain_pow2_single as hdlsrc\hdlcoderFocCurrentSingleTargetHdl\nfp_gain_pow2_single.vhd.

### Working on hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control/nfp_uminus_single as hdlsrc\hdlcoderFocCurrentSingleTargetHdl\nfp_uminus_single.vhd.

### Working on hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control/nfp_sincos_single as hdlsrc\hdlcoderFocCurrentSingleTargetHdl\nfp_sincos_single.vhd.

### Working on hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control as hdlsrc\hdlcoderFocCurrentSingleTargetHdl\FOC_Current_Control.vhd.

### Generating package file hdlsrc\hdlcoderFocCurrentSingleTargetHdl\FOC_Current_Control_pkg.vhd.

### Code Generation for 'hdlcoderFocCurrentSingleTargetHdl' completed.

### Generating HTML files for code generation report at <a href="matlab:hdlcoder.report.openDdg('C:\Users\user\OneDrive - MathWorks\Documents\MATLAB\ExampleManager\user.Dec27\hdlcoder-ex07589604\hdlsrc\hdlcoderFocCurrentSingleTargetHdl\html\hdlcoderFocCurrentSingleTargetHdl_codegen_rpt.html')">hdlcoderFocCurrentSingleTargetHdl_codegen_rpt.html</a>

### Creating HDL Code Generation Check Report file:///C:/Users/user/OneDrive%20-%20MathWorks/Documents/MATLAB/ExampleManager/user.Dec27/hdlcoder-ex07589604/hdlsrc/hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control_report.html

### HDL check for 'hdlcoderFocCurrentSingleTargetHdl' complete with 0 errors, 0 warnings, and 3 messages.

### HDL code generation complete.

The generated model infers fewer IP modules. You can see this change in the floating-point resource report.

Open the generated model to see the resource sharing results.

open_system('gm_hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control'); set_param('gm_hdlcoderFocCurrentSingleTargetHdl', 'SimulationCommand', 'update'); set_param('gm_hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control', 'ZoomFactor', 'FitSystem'); hilite_system('gm_hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control/crp_temp_shared'); hilite_system('gm_hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control/crp_temp_shared1'); hilite_system('gm_hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control/crp_temp_shared2'); hilite_system('gm_hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control/crp_temp_shared3'); hilite_system('gm_hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control/crp_temp_shared4'); hilite_system('gm_hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control/crp_temp_shared5');

Configure the IP Library

You can edit and control the customization configuration of the floating point IP libraries to meet your design requirements.

Create a mixed-mode floating-point target configuration object for the native floating-point and XILINX LOGICORE libraries.

fc = hdlcoder.createFloatingPointTargetConfig(VendorFloatingPointLibrary = 'XILINXLOGICORE');

In addition to the library name, library settings, and individual IP configuration settings for the native floating point library stored in the configuration object as Library, LibrarySettings, and IPConfig, respectively, the configuration object also has those properties for the XILINX LOGICORE library, specified as VendorLibrary, VendorLibrarySettings, and VendorIPConfig. View the configuration object, fc.

fc

fc =

FloatingPointTargetConfig with properties:

Library: 'NATIVEFLOATINGPOINT'

LibrarySettings: [1×1 fpconfig.NFPLatencyDrivenMode]

IPConfig: [1×1 hdlcoder.FloatingPointTargetConfig.IPConfig]

VendorLibrary: 'XILINXLOGICORE'

VendorLibrarySettings: [1×1 fpconfig.LatencyDrivenMode]

VendorIPConfig: [1×1 hdlcoder.FloatingPointTargetConfig.IPConfig]

The VendorLibrarySettings property contains library-wide settings for the vendor-specific floating-point library. Check the setting for XILINX LOGICORE library.

fc.VendorLibrarySettings

ans =

LatencyDrivenMode with properties:

LatencyStrategy: 'MIN'

Objective: 'SPEED'

The Objective property specifies the c_optimization parameter to XILINX LOGICORE. Set the Objective property to AREA.

fc.VendorLibrarySettings.Objective = 'AREA';

fc.VendorLibrarySettings

ans =

LatencyDrivenMode with properties:

LatencyStrategy: 'MIN'

Objective: 'AREA'

Vendor library settings are specific to the library. To see the settings for specific libraries, see hdlcoder.FloatingPointTargetConfig.

The VendorIPConfig property holds the IPConfig object for the vendor-specific library. This object has settings for individual IP modules that you can change by using the customize function, such as Latency and ExtraArgs.

Specify the latency for individual IP modules in the configuration object by using the customize function. HDL Coder uses the value of the Latency input argument that you set for code generation and optimizations.

fc.VendorIPConfig.customize('ADDSUB', 'SINGLE', 'Latency', 11); fc.VendorIPConfig

ans =

Name DataType MinLatency MaxLatency Latency ExtraArgs

__________ __________ __________ __________ _______ __________

{'ADDSUB'} {'DOUBLE'} 12 12 -1 {0×0 char}

{'ADDSUB'} {'SINGLE'} 12 12 11 {0×0 char}

{'DIV' } {'DOUBLE'} 57 57 -1 {0×0 char}

{'DIV' } {'SINGLE'} 28 28 -1 {0×0 char}

{'MUL' } {'DOUBLE'} 9 9 -1 {0×0 char}

{'MUL' } {'SINGLE'} 8 8 -1 {0×0 char}

{'RELOP' } {'DOUBLE'} 2 2 -1 {0×0 char}

{'RELOP' } {'SINGLE'} 2 2 -1 {0×0 char}

{'SQRT' } {'DOUBLE'} 57 57 -1 {0×0 char}

{'SQRT' } {'SINGLE'} 28 28 -1 {0×0 char}

The latency for the ADDSUB IP becomes 11 instead of the default value 12.

You can specify other IP-specific settings by setting the ExtraArgs property for individual IP modules. For example, HDL Coder calls XILINX LOGICORE to generate floating-point IP modules without using any DSP blocks by default. XILINX LOGICORE uses the c_mult_usage parameter to control DSP usage. In order to use DSP blocks, pass a different setting by using the ExtraArgs input argument to override the default behavior. Because the ExtraArgs string is appended to the default IP module generation parameters, it must comply with library setting syntax. Check the IP library documents for parameter usage and syntax.

fc.VendorIPConfig.customize('ADDSUB', 'SINGLE', 'ExtraArgs', 'CSET c_mult_usage=Full_Usage'); fc.VendorIPConfig

ans =

Name DataType MinLatency MaxLatency Latency ExtraArgs

__________ __________ __________ __________ _______ ________________________________

{'ADDSUB'} {'DOUBLE'} 12 12 -1 {0×0 char }

{'ADDSUB'} {'SINGLE'} 12 12 11 {'CSET c_mult_usage=Full_Usage'}

{'DIV' } {'DOUBLE'} 57 57 -1 {0×0 char }

{'DIV' } {'SINGLE'} 28 28 -1 {0×0 char }

{'MUL' } {'DOUBLE'} 9 9 -1 {0×0 char }

{'MUL' } {'SINGLE'} 8 8 -1 {0×0 char }

{'RELOP' } {'DOUBLE'} 2 2 -1 {0×0 char }

{'RELOP' } {'SINGLE'} 2 2 -1 {0×0 char }

{'SQRT' } {'DOUBLE'} 57 57 -1 {0×0 char }

{'SQRT' } {'SINGLE'} 28 28 -1 {0×0 char }

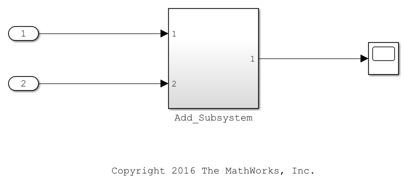

Open the model hdlcoder_targetIP_configuration and set the floating-point configuration object fc to the floating-point target configuration on the model.

open_system('hdlcoder_targetIP_configuration'); hdlset_param('hdlcoder_targetIP_configuration', 'FloatingPointTargetConfiguration', fc);

Run synthesis and mapping by using these commands to confirm the DSP block usage.

hWC = hdlcoder.WorkflowConfig('SynthesisTool','Xilinx ISE', ...

'TargetWorkflow','Generic ASIC/FPGA');

hWC.SkipPreRouteTimingAnalysis = true;

hWC.RunTaskAnnotateModelWithSynthesisResult = false;

hWC.GenerateRTLCode = true;

hWC.validate;

hdlcoder.runWorkflow('hdlcoder_targetIP_configuration/Add_Subsystem', hWC);See Also

hdlcoder.FloatingPointTargetConfig | createFloatingPointTargetConfig | hdlcoder.FloatingPointTargetConfig.IPConfig | customize