HDL-Codegenerierung

Sie können HDL Coder™ oder Filter Design HDL Coder™ verwenden, um ein DSP-Design auf FPGAs oder ASICs zu implementieren. Beide Produkte generieren synthetisierbaren und portablen VHDL®- und Verilog®- Code und erstellen VHDL-® und Verilog-Testumgebungen zum schnellen Simulieren, Testen und Verifizieren des generierten Codes.

HDL Coder — Generieren von Code aus Simulink oder MATLAB Designs. Unterstützte Blöcke der DSP System Toolbox™ und DSP HDL Toolbox umfassen Filter, mathematische und Signaloperationen sowie weitere Algorithmen, die für Ressourcennutzung und Leistung optimiert sind, wie die Blöcke FFT (DSP HDL Toolbox), Discrete FIR Filter (DSP HDL Toolbox) und NCO (DSP HDL Toolbox). Ein einfaches Beispiel zur Generierung von HDL-Code mit HDL Coder finden Sie unter Programmable FIR Filter for FPGA. Eine Einführung in die DSP HDL Toolbox™ finden Sie unter Implement FFT Algorithm for FPGA (DSP HDL Toolbox).

— Generieren von Code aus MATLAB-Filterdesigns. Sie können über die „Generate HDL“-Benutzeroberfläche oder die Befehlszeile auf die Funktionen zum Generieren von Code und Testumgebungen zugreifen. Diese Funktionen sind zudem in die Filter Designer App integriert. Ein Beispiel zur Generierung von HDL-Code mit Filter Design HDL Coder finden Sie unter .

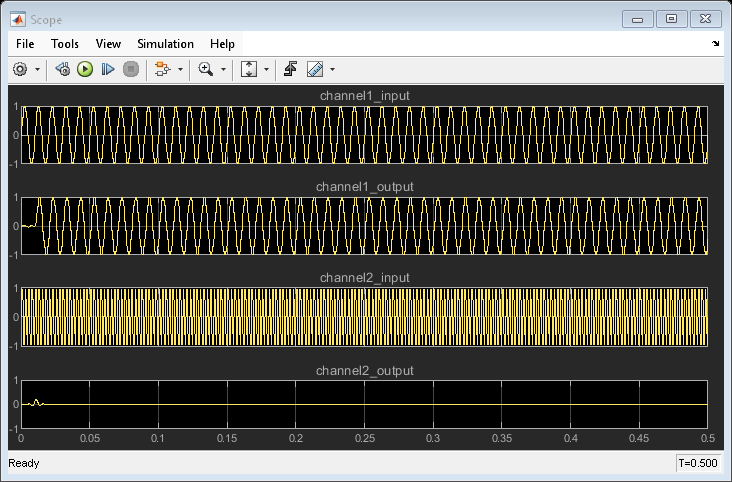

Um Ihre Designs in Simulink oder MATLAB zu debuggen, verwenden Sie den Logic Analyzer Wellenform-Viewer.

Simulink Visualisierungstool

| Logic Analyzer | Visualize, measure, and analyze transitions and states over time |

Themen

- Find Blocks That Support HDL Code Generation

Filter for blocks that support HDL code generation in the Simulink library browser and in documentation.

- High-Throughput HDL Algorithms (DSP HDL Toolbox)

Choose a block that supports frame-based processing for HDL code generation.

- HDL Filter Architectures

HDL code generation parameters to control speed and area tradeoffs in filter architectures.

- Subsystem Optimizations for Filters

Select resource sharing and pipeline optimization options.

- Visualize Multiple Signals Using Logic Analyzer

Visualize multiple signals of a programmable FIR filter by using the Logic Analyzer app.