Ports & Subsystems

hisl_0006: Usage of While Iterator blocks

| ID: Title | hisl_0006: Usage of While Iterator blocks | ||

|---|---|---|---|

| Description | To support bounded iterative behavior in the generated code when using the While Iterator block, set block parameter Maximum number of iterations to a positive integer value. | ||

| Note | When you use While Iterator subsystems, set the maximum number of iterations. If you use an unlimited number of iterations, the generated code might include infinite loops, which lead to execution-time overruns. To observe the iteration value during simulation and determine whether the loop reaches the maximum number of iterations, select the While Iterator block parameter Show iteration number port. If the loop reaches the maximum number of iterations, verify the output values of the While Iterator block. | ||

| Rationale | Support bounded iterative in the generated code. | ||

| Model Advisor Checks | Check usage of While Iterator blocks (Simulink Check) | ||

| References |

| ||

| Last Changed | R2026a | ||

hisl_0007: Usage of For Iterator or While Iterator subsystems

| ID: Title | hisl_0007: Usage of For Iterator or While Iterator subsystems | ||

|---|---|---|---|

| Description | To support unambiguous behavior, when using For Iterator Subsystem or While Iterator Subsystem, avoid using sample time-dependent blocks, such as integrators, filters, and transfer functions within the subsystems. | ||

| Rationale | Avoid ambiguous behavior from the subsystem. | ||

| Model Advisor Checks | Check usage of For and While Iterator subsystems (Simulink Check) | ||

| References |

| ||

| Last Changed | R2026a | ||

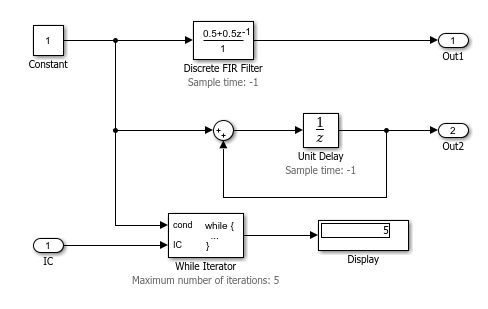

| Examples | The following example causes a warning: the Discrete FIR Filter block is time-dependent and is in a For or While Iterator subsystem.

| ||

hisl_0008: Usage of For Iterator Blocks

| ID: Title | hisl_0008: Usage of For Iterator blocks | ||

|---|---|---|---|

| Description | To support bounded iterative behavior in the generated code when using the For Iterator block, clear block parameter Set next i (iteration variable) externally and do one of the following: | ||

| A | Set block parameter Iteration

limit source to | ||

| B | When Iteration limit

source is set to | ||

| Notes | When you use the For Iterator block, feed the loop control variable with fixed (nonvariable) values to get a predictable number of loop iterations. Otherwise, a loop can result in unpredictable execution times and, in the case of external iteration variables, infinite loops that can lead to execution-time overruns. | ||

| Rationale | A, B | Support bounded iterative behavior in generated code. | |

| Model Advisor Checks | Check usage of For Iterator blocks (Simulink Check) | ||

| References |

| ||

| Last Changed | R2026a | ||

hisl_0010: Usage of If blocks and If Action Subsystem blocks

| ID: Title | hisl_0010: Usage of If blocks and If Action Subsystem blocks | ||

|---|---|---|---|

| Description | To support verifiable

generated code, when using the If block with nonempty

| ||

| A | Select block parameter Show else condition. | ||

| B | Connect the outports of the If block to If Action Subsystem blocks. | ||

| Prerequisites | hisl_0016: Usage of blocks that compute relational operators | ||

| Notes | The combination of

If and If Action Subsystem blocks

enable conditional execution based on input conditions. When there is

only an | ||

| Rationale | A, B | Support generation of verifiable code. | |

| Model Advisor Checks | Check usage of If blocks and If Action Subsystem blocks (Simulink Check) | ||

| References |

| ||

| Last Changed | R2026a | ||

| Examples |

Recommended: Elseif with Else

| ||

Not Recommended: No Else Path

| |||

Recommended: Only an If, no Else required

| |||

hisl_0011: Usage of Switch Case blocks and Action Subsystem blocks

| ID: Title | hisl_0011: Usage of Switch Case blocks and Action Subsystem blocks | ||

|---|---|---|---|

| Description | To support verifiable generated code, when using the Switch Case block: | ||

| A | Select block parameter Show default case. | ||

| B | Connect the outports of the Switch Case block to a Switch Case Action Subsystem block. | ||

| C | Use an integer data type or an enumeration value for the inputs to Switch Case blocks. | ||

| Prerequisites | hisl_0016: Usage of blocks that compute relational operators | ||

| Notes | The combination of Switch Case and If Action Subsystem blocks enable conditional execution based on input conditions. Provide a default path of execution in the form of a “Default” block. | ||

| Rationale | A, B, C | Support generation of verifiable code. | |

| Model Advisor Checks | Check usage of Switch Case blocks and Switch Case Action Subsystem blocks (Simulink Check) | ||

| References |

| ||

| Last Changed | R2026a | ||

| Examples | The following graphic displays an example of providing a default path of execution using a “Default” block.

| ||

hisl_0024: Inport interface definition

| ID: Title | hisl_0024: Inport interface definition |

|---|---|

| Description | To support strong data typing and unambiguous behavior of the model and the generated code, set parameters Data type, Port dimensions, and Sample time for each:

For export-function models, you can set

Sample time to

|

| Note | Using root-level Inport blocks without fully defined dimensions, sample times, or data type can lead to ambiguous simulation results. If you do not explicitly define these parameters, Simulink back-propagates dimensions, sample times, and data types from downstream blocks. Adhering to this guideline captures

reusable specifications (e.g. array of structures) as a

|

| Rationale |

|

| Model Advisor Checks | Check for root Inports with missing properties (Simulink Check) |

| References |

|

| Last Changed | R2026a |

hisl_0025: Design min/max specification of input interfaces

| ID: Title | hisl_0025: Design min/max specification of input interfaces |

|---|---|

| Description | Provide design minimum and maximum interface ranges for each

|

| Notes |

|

| Rationale | Support precise specification of the input interface. |

| Model Advisor Checks | Check for root Inports with missing range definitions (Simulink Check) |

| References |

|

| Last Changed | R2026a |

a These capabilities leverage design range information for different purposes. For more information, refer to the documentation for the tools you intend to use. | |

hisl_0026: Design min/max specification of output interfaces

| ID: Title | hisl_0026: Design min/max specification of output interfaces |

|---|---|

| Description | Provide minimum and maximum interface ranges for each

|

| Notes |

|

| Rationale | Support precise specification of the output interface. |

| Model Advisor Checks | Check for root Output ports with missing range definitions (Simulink Check) |

| References |

|

| Last Changed | R2026a |

a These capabilities leverage design range information for different purposes. For more information, refer to the documentation for the tools you intend to use. | |

hisl_0077: Outport interface definition

| ID: Title | hisl_0077: Outport interface definition |

|---|---|

| Description | To support strong data typing and unambiguous behavior of the model and the generated code, set the parameters Data type, Port dimensions, and Sample time for each:

For export-function models, you can set

Sample time to

|

| Note | Using root-level Outport blocks without fully defined dimensions, sample times, or data type can lead to ambiguous simulation results. |

| Rationale |

|

| Model Advisor Checks | Check for root Outports with missing properties (Simulink Check) |

| References |

|

| Last Changed | R2026a |