New FPGA Board Wizard

Using the New FPGA Board wizard, you can enter all the required information to add a board to the FPGA board list. This list applies to FPGA-in-the-Loop (FIL) workflows. Review FPGA Board Requirements before adding an FPGA board to make sure that it is compatible with the workflow for which you want to use it.

Several buttons in the New FPGA Board wizard help with navigation:

Back: Go to a previous page to review or edit data already entered.

Next: Go to next page when all requirements of current page have been satisfied.

Help: Open Doc Center, and display this topic.

Cancel: Exit New FPGA Board wizard. You can exit with or without saving the information from your session.

Adding Boards Once for Multiple Users

To add new boards globally, follow these instructions. To access a board added globally, all users must be using the same MATLAB® installation.

Create the following folder:

matlabroot/toolbox/shared/eda/board/boardfilesCopy the board description XML file to the

boardfilesfolder.After copying the XML file, restart MATLAB. The new board appears in the FPGA board list for the FIL workflow.

All boards under this folder show-up in the FPGA board list automatically for users with the same MATLAB installation. You do not need to use FPGA Board Manager to add these boards again.

The workflow for adding an FPGA board contains these steps:

Basic Information

Board Name: Enter a unique board name.

Device Information:

Vendor:

AMDorAlteraFamily: Family depends on the specified vendor. See the board specification file for applicable settings.

Device: Use the board specification file to select the correct device.

For AMD® boards only:

Package: Use the board specification file to select the correct package.

Speed: Use the board specification file to select the correct speed.

JTAG Chain Position: Value indicates the starting position for JTAG chain. Consult the board specification file for this information.

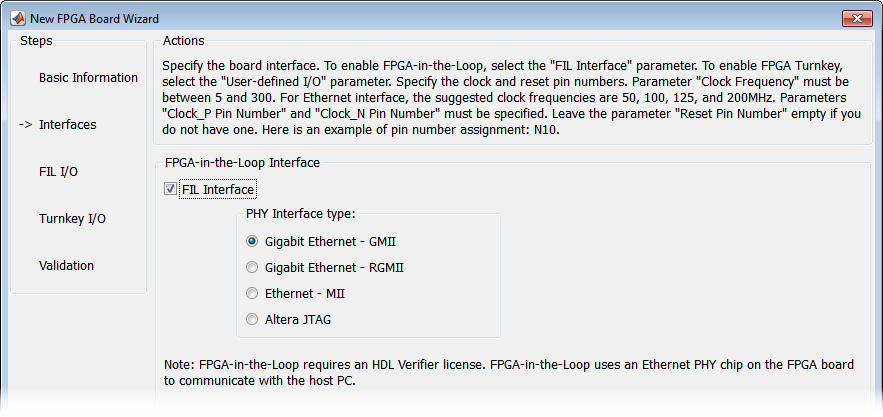

Interfaces

FIL Interface for Altera Boards

FPGA-in-the-Loop: To use this board with FIL, select FIL Interface.

Select one of the following PHY Interface types:

Gigabit Ethernet — GMII

Gigabit Ethernet — RGMII (Altera® boards only)

Gigabit Ethernet — SGMII (the SGMII option appears if you select a board from the Stratix® V or Stratix IV device families)

Ethernet — MII

Altera JTAG (Altera boards only)

Note

Not all interfaces are available for all boards. Availability depends on the board you selected in Basic Information.

FIL Interface for AMD Boards

FPGA-in-the-Loop Interface: To use this board with FIL, select FIL Interface.

Select one of the following PHY Interface types:

JTAG (via Digilent cable) (AMD boards only)

Ethernet — RMII

Note

Not all interfaces are available for all boards. Availability depends on the board you selected in Basic Information.

For more information on how to set up the JTAG connection for AMD boards, see JTAG with Digilent Cable Setup.

Limitations. When you simulate your FPGA design through a Digilent® JTAG cable, you cannot use any other debugging feature that requires access to the JTAG; for example, the Vivado® Logic Analyzer.

FPGA Input Clock and Reset

FPGA Input Clock — Clock details are required for both workflows. You can find all necessary information in the board specification file.

Clock Frequency — Must be from 5 through 300. For an Ethernet interface, the suggested clock frequencies are 50, 100, 125, and 200 MHz.

Clock Type —

Single_EndedorDifferential.Clock Pin Number (Single_Ended) — Must be specified. Example:

N10.Clock_P Pin Number (Differential) — Must be specified. Example:

E19.Clock_N Pin Number (Differential) — Must be specified. Example:

E18.Clock IO Standard — The programmable I/O Standard to use to configure input, output, or bi-directional ports. For example,

LVDS.

Reset (Optional) — If you want to indicate a reset, find the pin number and active level in the board specification file, and enter that information.

Reset Pin Number — Leave empty if you do not have one.

Active Level —

Active-LoworActive-High.Reset IO Standard — The programmable I/O Standard to use to configure input, output, or bi-directional ports. For example,

LVCMOS33.

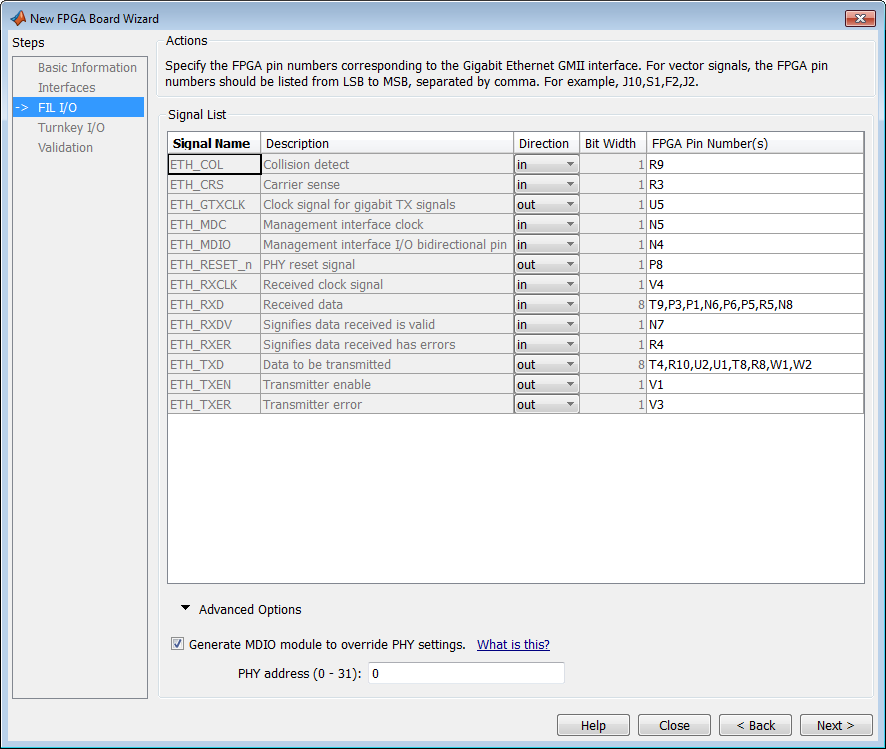

FIL I/O

When you select an Ethernet connection to your board, you must specify pins for the Ethernet signals on the FPGA.

Signal List: Provide all the FPGA pin numbers for the specified signals. You can find this information in the board specification file. For vector signals, list all pin numbers on the same line, separated by commas.

Note

If your PHY chip does not have the optional TX_ER pin, tie ETH_TXER to one of the unused pins on the FPGA.

Generate MDIO module to override PHY settings: See the next section on FPGA Board Management Data Input/Output Bus (MDIO) to determine when to use this feature. If you do select this option, enter the PHY address.

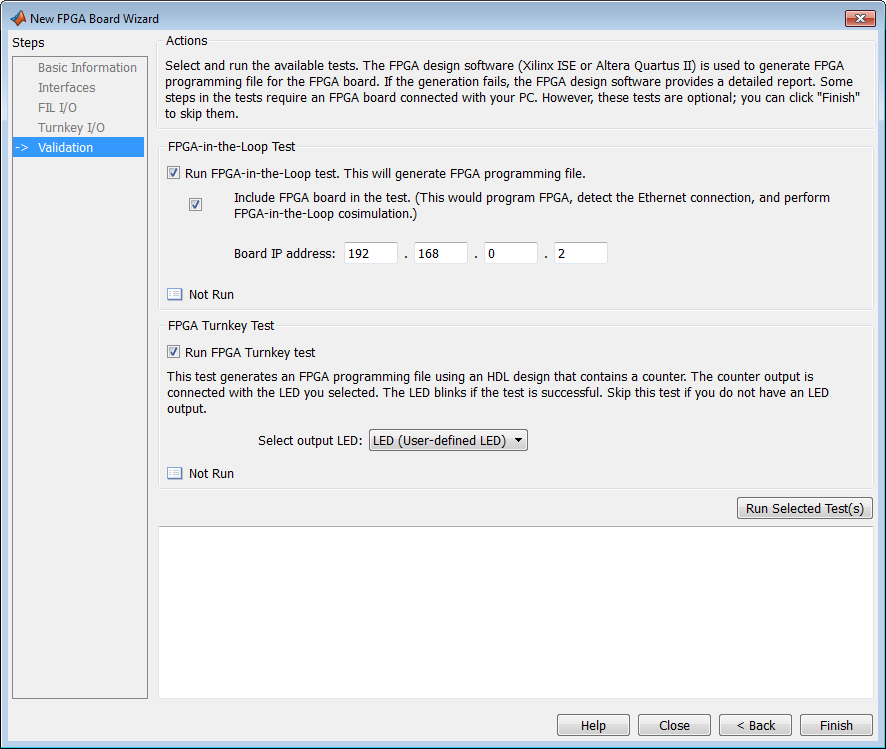

Validation

FPGA-in-the-Loop Test

Run FPGA-in-the-Loop test: Select to generate an FPGA programming file.

Include FPGA board in the test: (Optional) This selection program the FPGA with the generated programming file, detects the Ethernet connection (if selected), and performs FPGA-in-the-loop simulation.

Board IP address: (Ethernet connection only) Use this option for setting the board IP address if it is not the default IP address (192.168.0.2).

If necessary, change the computer IP address to a different subnet from 192.168.0.x when you set up the network adapter. If the default board IP address 192.168.0.2 is in use by another device, change the Board IP address according to the following guidelines:

The subnet address, typically the first 3 bytes of board IP address, must be the same as the host IP address.

The last byte of the board IP address must be different from the host IP address.

The board IP address must not conflict with the IP addresses of other computers.

For example, if the host IP address is 192.168.8.2, then you can use 192.168.8.3, if available.

Finish

When you have completed validation, click Finish. See Save Board Definition File.