Generate FPGA Block RAM from Lookup Tables

To map the lookup table blocks to random-access memory (RAM) to save area on your target Field Programmable Gate Array (FPGA) device, follow these guidelines.

Each guideline has a severity level that indicates the level of compliance requirements. For more information, see HDL Modeling Guidelines Severity Levels.

Guideline ID

2.3.1

Severity

Strongly Recommended

Description

To map lookup tables to a block RAM, you can use the Map lookup tables to RAM parameter located in the HDL Code Generation tab > Optimization > Pipelining tab in the Model Configuration Parameters dialog box. This parameter is selected on by default. The optimization inserts a Delay block that has a Delay length of 1 and ResetType set to none immediately following the Lookup Table block. This modeling pattern efficiently maps your design to a Block RAM on the FPGA. To use the map lookup tables to RAM option, you must:

Make sure that the Map lookup tables to RAM option is selected on for the model.

Specify the synthesis tool.

Alternatively, you can selectively enable this optimization for certain subsystems in your design by using the MapToRAM HDL Block Property and disabling the Map lookup tables to RAM option for the model or create the modeling pattern in your design that is the same as the pattern otherwise generated by the optimization.

For an example, open the model hdlcoder_LUT_BRAM_mapping.slx.

open_system('hdlcoder_LUT_BRAM_mapping') set_param('hdlcoder_LUT_BRAM_mapping','SimulationCommand','Update')

The Map lookup tables to RAM option is enabled on this model.

hdlget_param('hdlcoder_LUT_BRAM_mapping','LUTMapToRAM')

ans =

'on'

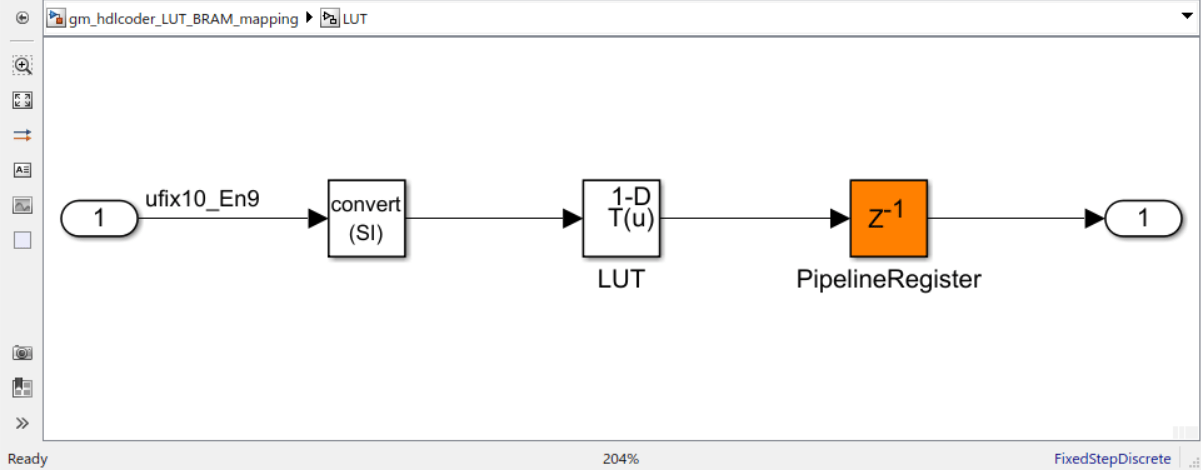

The LUT_BRAM Subsystem contains a 1-D Lookup Table block followed by a Delay block that has a Delay length of 1 and ResetType set to none.

open_system('hdlcoder_LUT_BRAM_mapping/LUT_BRAM')

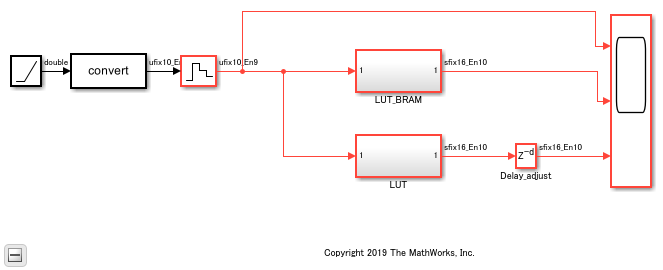

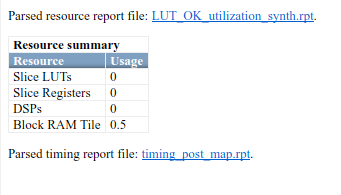

When you generate HDL code and synthesize the design on an FPGA, this modeling pattern efficiently maps to Block RAM. This figure displays the synthesis results for the LUT_BRAM Subsystem.

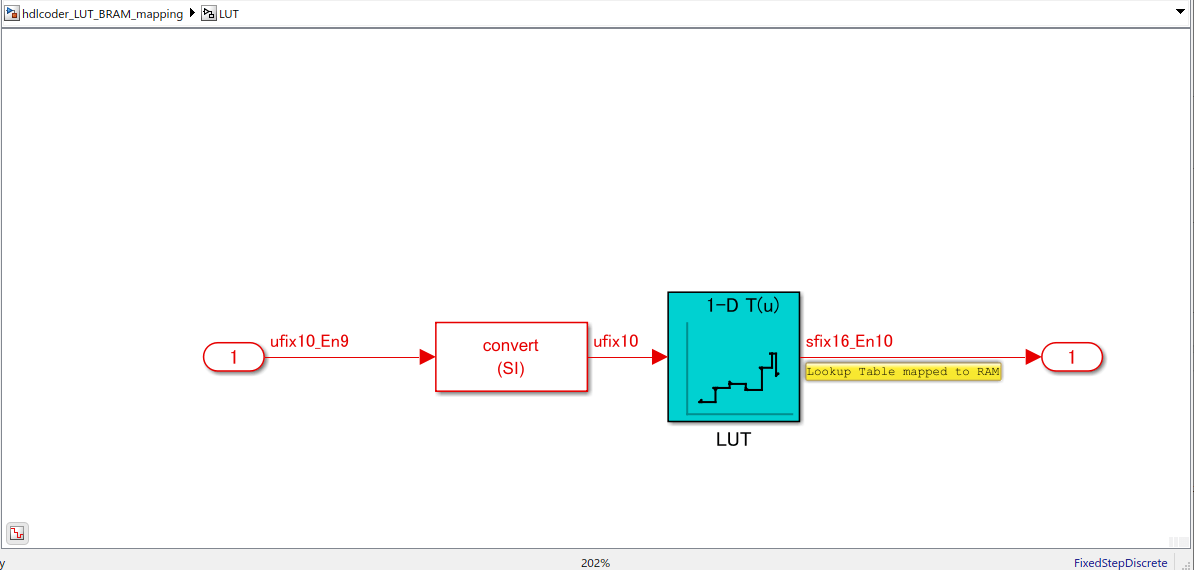

The LUT Subsystem in this model does not use this modeling pattern.

open_system('hdlcoder_LUT_BRAM_mapping/LUT')

Because the Map lookup tables to RAM option is enabled for this model, this subsystem still maps the logic to Block RAM. Click the MATLAB® script linked in the MATLAB command window to highlight lookup tables mapped to RAM in your model.

In order to map the lookup table to Block RAM, the generated model for the LUT Subsystem inserts a Delay block that has a Delay length of 1 and ResetType set to none immediately following the Lookup Table block.