Generate Black Box Interface for Subsystem

What Is a Black Box Interface?

A black box interface for a subsystem is a generated VHDL® component or Verilog® or SystemVerilog module that includes only the HDL input and output port definitions for the subsystem. By generating such a component, you can use a subsystem in your model to generate an interface to existing manually written HDL code, third-party IP, or other code generated by HDL Coder™.

Requirements

The black box implementation is available only for subsystem blocks below the level of the DUT. Virtual and atomic subsystem blocks of custom libraries that are below the level of the DUT also work with black box implementations.

Generate a Black Box Interface for Subsystem

To generate the interface, select the BlackBox implementation for one or more Subsystem blocks.

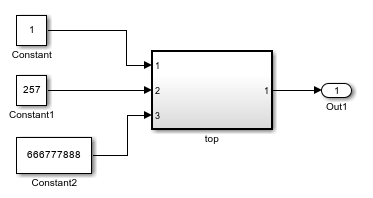

Consider the ex_blackbox_subsys model that contains a subsystem top, which is the device under test (DUT). Open the ex_blackbox_subsys model.

load_system("ex_blackbox_subsys.slx") open_system("ex_blackbox_subsys.slx")

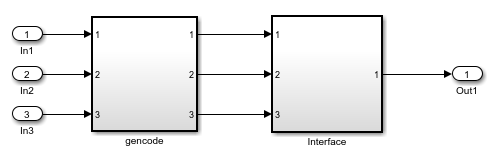

The subsystem top contains two lower-level subsystems.

open_system("ex_blackbox_subsys/top")

To generate HDL code from top model, with a black box interface from the Interface subsystem, follow these steps:

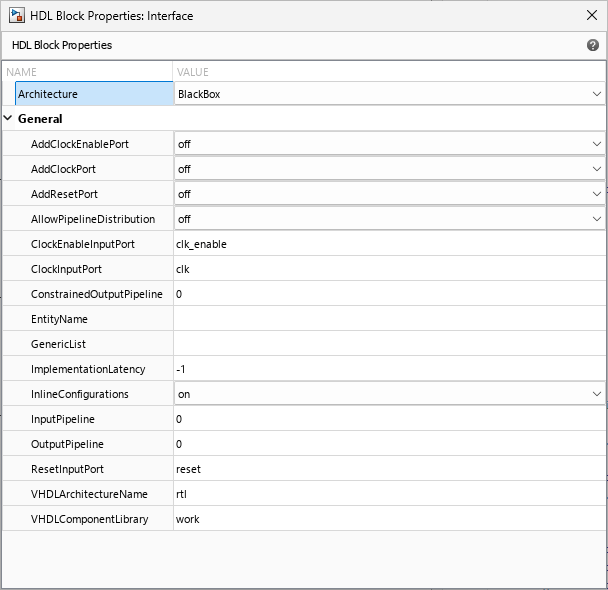

Right-click the

Interfacesubsystem. To add the HDL Coder app options to the context menu, point to Select Apps and click HDL Coder. Then, in the HDL Coder app section, select HDL Block Properties.Set Architecture to

BlackBox.

The following parameters are available for the black box implementation. The HDL block parameters available for the black box implementation enable you to customize the generated interface. See Customize Black Box or HDL Cosimulation Interface for information about these parameters.

To generate VHDL generic and a generic map for passing to a subsystem with a black box interface, set the GenericList parameter to {{'Param1','234'},{'Param2','"1"','STD_LOGIC'},{'Param3'','"1101"','STD_LOGIC_VECTOR(3 DOWNTO 0)'}} in the HDL block properties dialog box.

Alternatively, set the GenericList parameter for the black box Interface subsystem in the model by using the hdlset_param function. In the MATLAB Command Window, enter:

hdlset_param('ex_blackbox_subsys/top/Interface','GenericList',... '{{''Param1'',''234''},{''Param2'',''"1"'',''STD_LOGIC''},{''Param3'',''"1101"'',''STD_LOGIC_VECTOR(3 DOWNTO 0)''}}');

The input to the GenericList block parameter is a cell array variable that contains three cell arrays, each with two or three character arrays. These character arrays represent the name, value, and data type of a VHDL generic. In this example, the data type of Param1 is an integer, Param2 is a STD_LOGIC, and Param3 is a STD_LOGIC_VECTOR. Use double quotes to denote scalar and vector values. For more information about the GenericList parameter syntax, see Customize Black Box or HDL Cosimulation Interface.

Generate Code for a Black Box Subsystem Implementation

When you generate code for the DUT in the ex_blackbox_subsys model, the following messages appear:

makehdl("ex_blackbox_subsys/top")### Working on the model ex_blackbox_subsys ### Generating HDL for ex_blackbox_subsys/top ### Using the config set for model ex_blackbox_subsys for HDL code generation parameters. ### Running HDL checks on the model 'ex_blackbox_subsys'. ### Begin compilation of the model 'ex_blackbox_subsys'... ### Working on the model 'ex_blackbox_subsys'... ### Working on... GenerateModel ### Begin model generation 'gm_ex_blackbox_subsys'... ### Rendering DUT with optimization related changes (IO, Area, Pipelining)... ### Model generation complete. ### Generated model saved at hdlsrc/ex_blackbox_subsys/gm_ex_blackbox_subsys.slx ### Begin VHDL Code Generation for 'ex_blackbox_subsys'. ### Working on ex_blackbox_subsys/top/gencode as hdlsrc/ex_blackbox_subsys/gencode.vhd. ### Working on ex_blackbox_subsys/top as hdlsrc/ex_blackbox_subsys/top.vhd. ### Code Generation for 'ex_blackbox_subsys' completed. ### Generating HTML files for code generation report at index.html ### Creating HDL Code Generation Check Report top_report.html ### HDL check for 'ex_blackbox_subsys' complete with 0 errors, 1 warnings, and 0 messages. ### HDL code generation complete.

In the progress messages, observe that the gencode subsystem generates a separate file, gencode.vhd, for its VHDL entity definition. The Interface subsystem does not generate such a file. The interface code for this subsystem is in top.vhd, generated from ex_blackbox_subsys/top. The following code listing shows the component definition and instantiation generated for the Interface subsystem.

COMPONENT Interface

GENERIC( Param1 : integer;

Param2 : STD_LOGIC;

Param3 : STD_LOGIC_VECTOR(3 DOWNTO 0)

);

PORT( clk : IN std_logic;

clk_enable : IN std_logic;

reset : IN std_logic;

In1 : IN std_logic_vector(7 DOWNTO 0); -- uint8

In2 : IN std_logic_vector(15 DOWNTO 0); -- uint16

In3 : IN std_logic_vector(31 DOWNTO 0); -- uint32

Out1 : OUT std_logic_vector(31 DOWNTO 0) -- uint32

);

END COMPONENT;

...

u_Interface : Interface

GENERIC MAP( Param1 => 234,

Param2 => "1",

Param3 => "1101"

)

PORT MAP( clk => clk,

clk_enable => enb_const_rate,

reset => reset,

In1 => gencode_out1, -- uint8

In2 => gencode_out2, -- uint16

In3 => gencode_out3, -- uint32

Out1 => Interface_out1 -- uint32

);

enb_const_rate <= clk_enable;

Out1 <= Interface_out1;

By default, the black box interface generated for subsystems includes clock, clock enable, and reset ports. Customize Black Box or HDL Cosimulation Interface describes how you can rename or suppress generation of these signals, and customize other aspects of the generated interface.

Limitations

You cannot use bidirectional ports for masked subsystems with the Architecture HDL Block property set to

BlackBox.If you place a black box subsystem containing a DocBlock inside another black box subsystem, HDL Coder does not integrate the HDL code from the inner DocBlock during code generation.

If a black box subsystem contains a DocBlock with custom

packagedeclarations, HDL Coder does not include those package data types in the generated interface code.Even if you select the MinimizeGlobalResets parameter, HDL Coder generates reset logic if Subsystem blocks with

BlackBoxHDL architecture requires a reset signal.You cannot perform delay balancing if a subsystem with

BlackBoxarchitecture has the ImplementationLatency block property set to a negative value.You cannot use clock-rate pipelining for subsystems or Model blocks with the Architecture HDL Block property set to

BlackBox.You cannot use Bus Element ports for masked subsystems with the Architecture HDL Block property set to

BlackBox.