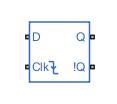

D Flip-Flop

Libraries:

Simscape /

Electrical /

Integrated Circuits /

Logic

Description

The D Flip-Flop block implements a behavioral model of a

clocked D flip-flop. The block stores a one-bit value, either 0

(low) or 1 (high).

The block has two input ports: the data pin D and the clock pin Clk. The block transfers the data at D to the output pin Q. The output updates only when the clock signal transitions on the active edge of the clock. Otherwise, the block holds the output in its previous state.

You can update the output on the falling or rising edge of the clock. To update the output

only when the clock transitions from high to low, set

the Edge trigger parameter to Falling. To

update the output only when the clock transitions from low to

high, set the Edge trigger parameter to

Rising. This truth table summarizes the logic levels at the

inputs and output. The subscript n represents the value at the current

clock cycle and n-1 represents the value at the previous clock cycle. The

logic level at the inverted output pin !Q is the inverse of the logic level at

Q.

| Edge trigger parameter value | Clkn-1 | Clkn | Qn |

|---|---|---|---|

Falling | 0 | 0 | Qn-1 |

Falling | 0 | 1 | Qn-1 |

Falling | 1 | 0 | Dn |

Falling | 1 | 1 | Qn-1 |

Rising | 0 | 0 | Qn-1 |

Rising | 0 | 1 | Dn |

Rising | 1 | 0 | Qn-1 |

Rising | 1 | 1 | Qn-1 |

To specify the logic level at Q at the start of the simulation, in the

Initial Targets section, set the value of the Output

logic parameter to 0 or 1.

For more information about initial targets, see Set Priority and Initial Target for Block Variables.

The gate inputs have an infinite resistance and a finite or zero capacitance.

If the gate voltage is greater than the threshold voltage, then the block takes the logic

level at the input as 1. Otherwise, the block takes the logic level at the

input as 0. The block calculates the threshold voltage as the average of

the Low level input voltage and the High level input

voltage parameter values.

The gate output depends on the Output current-voltage relationship

parameter. Set this parameter to Linear for faster simulation and

Quadratic for more accurate results. For most models, use the

Linear option. You can use the

Quadratic option to validate the results that you obtain using

the simpler linear model. For more information, see Selecting the Output Model for Logic Blocks.

If you set the Output current-voltage relationship parameter to

Linear:

If the logic level at the Q port is

0, the output voltage is equal to the Low level output voltage parameter value.If the logic level at the Q port is

1, the output voltage is equal to the High level output voltage parameter value.The resistor-capacitor time constant of the gate output capacitor is equal to the Propagation delay parameter value.

If you set the Output current-voltage relationship parameter to

Quadratic:

The output voltage is a function of the output current. For zero-load current:

If the logic level at the Q port is

0, the output voltage is zero.If the logic level at the Q port is

1, the output voltage is equal to the Supply voltage parameter value.

The gate input demand lags to approximate the Propagation delay parameter value.

For more information, see Quadratic Model Output and Parameters.

Plot Input and Output Waveforms

You can plot the input and output voltage waveforms of the D Flip-Flop block without building a complete model. Use the plots to explore the impact of your parameter choices on device characteristics. If you parameterize the block from a data sheet, you can compare your plots to the data sheet to check that you parameterized the block correctly. If you have a complete working model but do not know which manufactured part to use, you can compare your plots to data sheets to help you decide.

To plot the basic characteristics, in the Utilities section, click the Plot button next to the Basic characteristics parameter. (since R2026a)

Before R2026a: right-click the block and select Electrical > Basic Characteristics from the context menu.

Note

The plots you create using the Basic characteristics parameter do not show the effect of the Propagation delay parameter on the output voltage of logic blocks.

For more information, see Plot Basic Input-Output Voltage Characteristics of Logic Gates.

Assumptions and Limitations

To improve simulation speed, the block does not model all the internal metal-oxide-semiconductor field-effect transistor (MOSFET) devices in the gate individually. The block therefore does not accurately model the response of the gate to input noise and input voltages that are close to the threshold voltage.

If you are modeling a circuit that has a feedback path around a set of logic gates, you must set the Propagation delay parameter to a nonzero value on one or more of the gates.