Separate Rate Transition Block Code from Algorithm Code

This example shows how to generate code for Rate Transition blocks that is separate from code produced for the model algorithm. By default, Rate Transition block code and data are inlined with algorithm code and data. Separating the Rate Transition block code from algorithm code enables you to independently analyze, optimize, and test Rate Transition block and algorithm code. When you choose to separate the Rate Transition block code, the generated code contains separate get and set functions that the model_step entry-point functions call and a dedicated structure for rate transition state data.

Example Model

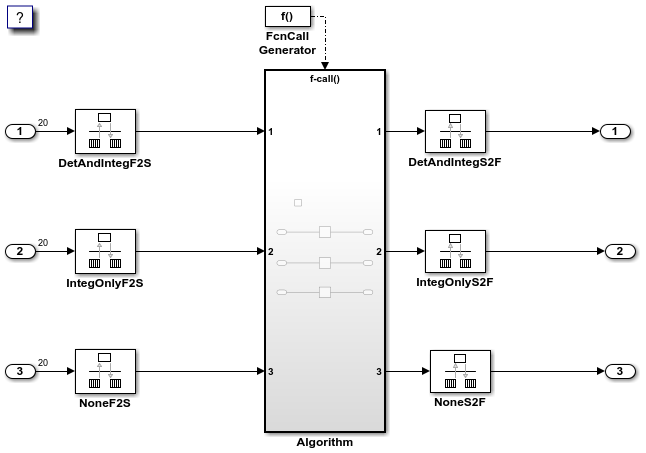

Open the example model MultirateMultitaskingRateTransitions.

model = "MultirateMultitaskingRateTransitions";

open_system(model);

Configure Model for Separate Rate Transition Block Code Generation

Set model configuration parameter Rate Transition block code to Function.

set_param(model,'RateTransitionBlockCode','Function');

Generate and Review Separate Rate Transition Block Code

Generate code for the model.

slbuild(model);

### Searching for referenced models in model 'MultirateMultitaskingRateTransitions'. ### Total of 1 models to build. ### Starting build procedure for: MultirateMultitaskingRateTransitions ### Successful completion of build procedure for: MultirateMultitaskingRateTransitions Build Summary Top model targets: Model Build Reason Status Build Duration ======================================================================================================================================= MultirateMultitaskingRateTransitions Information cache folder or artifacts were missing. Code generated and compiled. 0h 0m 10.706s 1 of 1 models built (0 models already up to date) Build duration: 0h 0m 11.247s

The code generator does not separate the code and data for Rate Transition blocks that operate on variable-size signals or are inside of a For Each Subsystem block.

When generating separate code for Rate Transition blocks, the code generator places the rate transition state data in its own structure in the file MultirateMultitaskingRateTransitions_rtb.h.

currentDir = pwd; hfile = fullfile(currentDir,'MultirateMultitaskingRateTransitions_ert_rtw', ... 'MultirateMultitaskingRateTransitions_rtb.h'); coder.example.extractLines(hfile,'typedef struct {','} RTB', 1, 1);

typedef struct {

real_T DetAndIntegS2F_Buffer0[20]; /* '<Root>/DetAndIntegS2F' */

real_T DetAndIntegS2F_Buffer1[20]; /* '<Root>/DetAndIntegS2F' */

volatile real_T IntegOnlyS2F_Buffer[40];/* '<Root>/IntegOnlyS2F' */

real_T DetAndIntegF2S_Buffer[20]; /* '<Root>/DetAndIntegF2S' */

volatile real_T IntegOnlyF2S_Buffer0[20];/* '<Root>/IntegOnlyF2S' */

volatile int8_T IntegOnlyS2F_ActiveBufIdx;/* '<Root>/IntegOnlyS2F' */

volatile int8_T IntegOnlyF2S_semaphoreTaken;/* '<Root>/IntegOnlyF2S' */

} RTB;

The file MultirateMultitaskingRateTransitions_rtb.h also declares rate transition get and set functions.

hfile=fullfile(currentDir, 'MultirateMultitaskingRateTransitions_ert_rtw',... 'MultirateMultitaskingRateTransitions_rtb.h'); coder.example.extractLines(hfile,'extern void MultirateMul_DetAndIntegS2F_get',... 'extern void MultirateMulti_IntegOnlyS2F_set', 1, 1);

extern void MultirateMul_DetAndIntegS2F_get(real_T DetAndIntegS2F_value[20]); extern void MultirateMulti_IntegOnlyS2F_get(real_T IntegOnlyS2F_value[20]); extern void MultirateMul_DetAndIntegF2S_set(const real_T DetAndIntegF2S_value[20]); extern void MultirateMulti_IntegOnlyF2S_set(const real_T IntegOnlyF2S_value[20]); extern void MultirateMul_DetAndIntegF2S_get(real_T DetAndIntegF2S_value[20]); extern void MultirateMulti_IntegOnlyF2S_get(real_T IntegOnlyF2S_value[20]); extern void MultirateMul_DetAndIntegS2F_set(const real_T DetAndIntegS2F_value[20]); extern void MultirateMulti_IntegOnlyS2F_set(const real_T IntegOnlyS2F_value[20]);

The rate transition get and set functions, which contain the Rate Transition block code, are defined in the file MultirateMultitaskingRateTransitions_rtb.c.

cfile=fullfile(currentDir, 'MultirateMultitaskingRateTransitions_ert_rtw',... 'MultirateMultitaskingRateTransitions_rtb.c'); coder.example.extractLines(cfile,... '/* RateTransition function MultirateMul_DetAndIntegS2F_get',... '* File trailer for generated code',1,0);

/* RateTransition function MultirateMul_DetAndIntegS2F_get */

extern void MultirateMul_DetAndIntegS2F_get(real_T DetAndIntegS2F_value[20])

{

/* RateTransition: '<Root>/DetAndIntegS2F' */

if (rtM->Timing.RateInteraction.TID0_1 == 1) {

memcpy(&rtRTB.DetAndIntegS2F_Buffer1[0], &rtRTB.DetAndIntegS2F_Buffer0[0],

20U * sizeof(real_T));

}

memcpy(&DetAndIntegS2F_value[0], &rtRTB.DetAndIntegS2F_Buffer1[0], 20U *

sizeof(real_T));

/* End of RateTransition: '<Root>/DetAndIntegS2F' */

}

/* RateTransition function MultirateMulti_IntegOnlyS2F_get */

extern void MultirateMulti_IntegOnlyS2F_get(real_T IntegOnlyS2F_value[20])

{

int32_T i;

int32_T tmp;

/* RateTransition: '<Root>/IntegOnlyS2F' */

tmp = rtRTB.IntegOnlyS2F_ActiveBufIdx * 20;

for (i = 0; i < 20; i++) {

IntegOnlyS2F_value[i] = rtRTB.IntegOnlyS2F_Buffer[i + tmp];

}

/* End of RateTransition: '<Root>/IntegOnlyS2F' */

}

/* RateTransition function MultirateMul_DetAndIntegF2S_set */

extern void MultirateMul_DetAndIntegF2S_set(const real_T DetAndIntegF2S_value[20])

{

/* RateTransition: '<Root>/DetAndIntegF2S' */

if (rtM->Timing.RateInteraction.TID0_1 == 1) {

memcpy(&rtRTB.DetAndIntegF2S_Buffer[0], &DetAndIntegF2S_value[0], 20U *

sizeof(real_T));

}

/* End of RateTransition: '<Root>/DetAndIntegF2S' */

}

/* RateTransition function MultirateMulti_IntegOnlyF2S_set */

extern void MultirateMulti_IntegOnlyF2S_set(const real_T IntegOnlyF2S_value[20])

{

int32_T i;

/* RateTransition: '<Root>/IntegOnlyF2S' */

if (rtRTB.IntegOnlyF2S_semaphoreTaken == 0) {

for (i = 0; i < 20; i++) {

rtRTB.IntegOnlyF2S_Buffer0[i] = IntegOnlyF2S_value[i];

}

}

/* End of RateTransition: '<Root>/IntegOnlyF2S' */

}

/* RateTransition function MultirateMul_DetAndIntegF2S_get */

extern void MultirateMul_DetAndIntegF2S_get(real_T DetAndIntegF2S_value[20])

{

/* RateTransition: '<Root>/DetAndIntegF2S' */

memcpy(&DetAndIntegF2S_value[0], &rtRTB.DetAndIntegF2S_Buffer[0], 20U * sizeof

(real_T));

}

/* RateTransition function MultirateMulti_IntegOnlyF2S_get */

extern void MultirateMulti_IntegOnlyF2S_get(real_T IntegOnlyF2S_value[20])

{

int32_T i;

/* RateTransition: '<Root>/IntegOnlyF2S' */

rtRTB.IntegOnlyF2S_semaphoreTaken = 1;

for (i = 0; i < 20; i++) {

IntegOnlyF2S_value[i] = rtRTB.IntegOnlyF2S_Buffer0[i];

}

rtRTB.IntegOnlyF2S_semaphoreTaken = 0;

/* End of RateTransition: '<Root>/IntegOnlyF2S' */

}

/* RateTransition function MultirateMul_DetAndIntegS2F_set */

extern void MultirateMul_DetAndIntegS2F_set(const real_T DetAndIntegS2F_value[20])

{

/* RateTransition: '<Root>/DetAndIntegS2F' */

memcpy(&rtRTB.DetAndIntegS2F_Buffer0[0], &DetAndIntegS2F_value[0], 20U *

sizeof(real_T));

}

/* RateTransition function MultirateMulti_IntegOnlyS2F_set */

extern void MultirateMulti_IntegOnlyS2F_set(const real_T IntegOnlyS2F_value[20])

{

int32_T i;

/* RateTransition: '<Root>/IntegOnlyS2F' */

for (i = 0; i < 20; i++) {

rtRTB.IntegOnlyS2F_Buffer[i + (rtRTB.IntegOnlyS2F_ActiveBufIdx == 0) * 20] =

IntegOnlyS2F_value[i];

}

rtRTB.IntegOnlyS2F_ActiveBufIdx = (int8_T)(rtRTB.IntegOnlyS2F_ActiveBufIdx ==

0);

/* End of RateTransition: '<Root>/IntegOnlyS2F' */

}

/*

The model entry-point functions MultirateMultitaskingRateTransitions_step0 and MultirateMultitaskingRateTransitions_step1 in the file MultirateMultitaskingRateTransitions.c call the rate transition get and set functions that are defined in MultirateMultitaskingRateTransitions_rtb.c.

cfile=fullfile(currentDir, 'MultirateMultitaskingRateTransitions_ert_rtw', ... 'MultirateMultitaskingRateTransitions.c'); coder.example.extractLines(cfile,'/* Model step function for TID0',... 'rtDW.Integrator3_PREV_U[i] = rtU.In3[i];',1,0);

/* Model step function for TID0 */

void MultirateMultitaskingRateTransitions_step0(void) /* Sample time: [0.0005s, 0.0s] */

{

/* Update the flag to indicate when data transfers from

* Sample time: [0.0005s, 0.0s] to Sample time: [0.001s, 0.0s] */

(rtM->Timing.RateInteraction.TID0_1)++;

if ((rtM->Timing.RateInteraction.TID0_1) > 1) {

rtM->Timing.RateInteraction.TID0_1 = 0;

}

/* Outport: '<Root>/Out1' incorporates:

* RateTransition: '<Root>/DetAndIntegS2F'

*/

MultirateMul_DetAndIntegS2F_get(rtY.Out1);

/* RateTransition: '<Root>/IntegOnlyS2F' */

MultirateMulti_IntegOnlyS2F_get(rtY.Out2);

/* Outport: '<Root>/Out3' incorporates:

* RateTransition: '<Root>/NoneS2F'

*/

memcpy(&rtY.Out3[0], &rtDW.OutportBufferForOut3[0], 20U * sizeof(real_T));

/* RateTransition: '<Root>/DetAndIntegF2S' incorporates:

* Inport: '<Root>/In1'

*/

MultirateMul_DetAndIntegF2S_set(rtU.In1);

/* RateTransition: '<Root>/IntegOnlyF2S' incorporates:

* Inport: '<Root>/In2'

*/

MultirateMulti_IntegOnlyF2S_set(rtU.In2);

}

/* Model step function for TID1 */

void MultirateMultitaskingRateTransitions_step1(void) /* Sample time: [0.001s, 0.0s] */

{

real_T rtb_DetAndIntegF2S[20];

real_T rtb_IntegOnlyF2S[20];

real_T Integrator3_DSTATE;

real_T tmp;

int32_T i;

uint32_T Algorithm_ELAPS_T;

/* RateTransition: '<Root>/DetAndIntegF2S' */

MultirateMul_DetAndIntegF2S_get(rtb_DetAndIntegF2S);

/* RateTransition: '<Root>/IntegOnlyF2S' */

MultirateMulti_IntegOnlyF2S_get(rtb_IntegOnlyF2S);

/* FunctionCallGenerator: '<Root>/FcnCall Generator' incorporates:

* SubSystem: '<Root>/Algorithm'

*/

if (rtDW.bitsForTID1.Algorithm_RESET_ELAPS_T) {

Algorithm_ELAPS_T = 0U;

} else {

Algorithm_ELAPS_T = rtM->Timing.clockTick1 - rtDW.Algorithm_PREV_T;

}

rtDW.Algorithm_PREV_T = rtM->Timing.clockTick1;

rtDW.bitsForTID1.Algorithm_RESET_ELAPS_T = 0U;

/* DiscreteIntegrator: '<S1>/Integrator1' */

tmp = 0.001 * (real_T)Algorithm_ELAPS_T;

for (i = 0; i < 20; i++) {

/* DiscreteIntegrator: '<S1>/Integrator1' */

if (rtDW.Integrator1_SYSTEM_ENABLE == 0) {

/* DiscreteIntegrator: '<S1>/Integrator1' */

rtDW.Integrator1_DSTATE[i] += tmp * rtDW.Integrator1_PREV_U[i];

}

/* DiscreteIntegrator: '<S1>/Integrator2' */

if (rtDW.Integrator2_SYSTEM_ENABLE == 0) {

/* DiscreteIntegrator: '<S1>/Integrator2' */

rtDW.Integrator2_DSTATE[i] += tmp * rtDW.Integrator2_PREV_U[i];

}

/* End of DiscreteIntegrator: '<S1>/Integrator2' */

/* DiscreteIntegrator: '<S1>/Integrator3' */

Integrator3_DSTATE = rtDW.Integrator3_DSTATE[i];

if (rtDW.Integrator3_SYSTEM_ENABLE == 0) {

/* DiscreteIntegrator: '<S1>/Integrator3' */

Integrator3_DSTATE += tmp * rtDW.Integrator3_PREV_U[i];

}

/* DiscreteIntegrator: '<S1>/Integrator3' */

rtDW.Integrator3_DSTATE[i] = Integrator3_DSTATE;

/* SignalConversion generated from: '<S1>/Out3' */

rtDW.OutportBufferForOut3[i] = Integrator3_DSTATE;

/* Update for DiscreteIntegrator: '<S1>/Integrator1' */

rtDW.Integrator1_PREV_U[i] = rtb_DetAndIntegF2S[i];

/* Update for DiscreteIntegrator: '<S1>/Integrator2' */

rtDW.Integrator2_PREV_U[i] = rtb_IntegOnlyF2S[i];

/* Update for DiscreteIntegrator: '<S1>/Integrator3' incorporates:

* Inport: '<Root>/In3'

* RateTransition: '<Root>/NoneF2S'

*/

Configure Model for Inlined Rate Transition Block Code Generation

Compare the code that is separated to code that the code generator produces when inlining rate transition code. Set model configuration parameter Rate Transition block code to Inline.

set_param(model,'RateTransitionBlockCode','Inline');

Generate and Review Inlined Rate Transition Block Code

Reenerate code for the model.

slbuild(model);

### Searching for referenced models in model 'MultirateMultitaskingRateTransitions'. ### Total of 1 models to build. ### Starting build procedure for: MultirateMultitaskingRateTransitions ### Successful completion of build procedure for: MultirateMultitaskingRateTransitions Build Summary Top model targets: Model Build Reason Status Build Duration =================================================================================================================== MultirateMultitaskingRateTransitions Generated code was out of date. Code generated and compiled. 0h 0m 8.8419s 1 of 1 models built (0 models already up to date) Build duration: 0h 0m 9.4367s

When generating inlined code for Rate Transition blocks, the code generator places the rate transition state data in a global state structure in the file MultirateMultitaskingRateTransitions.h.

hfile=fullfile(currentDir, 'MultirateMultitaskingRateTransitions_ert_rtw',... 'MultirateMultitaskingRateTransitions.h'); coder.example.extractLines(hfile,... '/* Block signals and states (default storage) for system', '} DW;', 1, 1);

/* Block signals and states (default storage) for system '<Root>' */

typedef struct {

real_T DetAndIntegS2F[20]; /* '<Root>/DetAndIntegS2F' */

real_T OutportBufferForOut3[20]; /* '<S1>/Integrator3' */

real_T Integrator1_DSTATE[20]; /* '<S1>/Integrator1' */

real_T Integrator2_DSTATE[20]; /* '<S1>/Integrator2' */

real_T Integrator3_DSTATE[20]; /* '<S1>/Integrator3' */

real_T DetAndIntegS2F_Buffer0[20]; /* '<Root>/DetAndIntegS2F' */

volatile real_T IntegOnlyS2F_Buffer[40];/* '<Root>/IntegOnlyS2F' */

real_T DetAndIntegF2S_Buffer[20]; /* '<Root>/DetAndIntegF2S' */

volatile real_T IntegOnlyF2S_Buffer0[20];/* '<Root>/IntegOnlyF2S' */

real_T Integrator1_PREV_U[20]; /* '<S1>/Integrator1' */

real_T Integrator2_PREV_U[20]; /* '<S1>/Integrator2' */

real_T Integrator3_PREV_U[20]; /* '<S1>/Integrator3' */

uint32_T Algorithm_PREV_T; /* '<Root>/Algorithm' */

struct {

uint_T Algorithm_RESET_ELAPS_T : 1;/* '<Root>/Algorithm' */

} bitsForTID1;

volatile int8_T IntegOnlyS2F_ActiveBufIdx;/* '<Root>/IntegOnlyS2F' */

volatile int8_T IntegOnlyF2S_semaphoreTaken;/* '<Root>/IntegOnlyF2S' */

uint8_T Integrator1_SYSTEM_ENABLE; /* '<S1>/Integrator1' */

uint8_T Integrator2_SYSTEM_ENABLE; /* '<S1>/Integrator2' */

uint8_T Integrator3_SYSTEM_ENABLE; /* '<S1>/Integrator3' */

} DW;

The code for the rate transition get and set functions is inlined in entry-point funcitons MultirateMultitaskingRateTransitions_step0 and MultirateMultitaskingRateTransitions_step1, which are defined in the file MultirateMultitaskingRateTransitions.c.

cfile=fullfile(currentDir, 'MultirateMultitaskingRateTransitions_ert_rtw',... 'MultirateMultitaskingRateTransitions.c'); coder.example.extractLines(cfile,'/* End of RateTransition:',... '/* Model initialize function */', 1, 0);

/* End of RateTransition: '<Root>/DetAndIntegS2F' */

/* Outport: '<Root>/Out1' */

memcpy(&rtY.Out1[0], &rtDW.DetAndIntegS2F[0], 20U * sizeof(real_T));

/* RateTransition: '<Root>/IntegOnlyS2F' */

i = rtDW.IntegOnlyS2F_ActiveBufIdx * 20;

for (i_0 = 0; i_0 < 20; i_0++) {

rtY.Out2[i_0] = rtDW.IntegOnlyS2F_Buffer[i_0 + i];

}

/* End of RateTransition: '<Root>/IntegOnlyS2F' */

/* Outport: '<Root>/Out3' */

memcpy(&rtY.Out3[0], &rtDW.OutportBufferForOut3[0], 20U * sizeof(real_T));

/* RateTransition: '<Root>/DetAndIntegF2S' incorporates:

* Inport: '<Root>/In1'

*/

if (rtM->Timing.RateInteraction.TID0_1 == 1) {

memcpy(&rtDW.DetAndIntegF2S_Buffer[0], &rtU.In1[0], 20U * sizeof(real_T));

}

/* End of RateTransition: '<Root>/DetAndIntegF2S' */

/* RateTransition: '<Root>/IntegOnlyF2S' incorporates:

* Inport: '<Root>/In2'

*/

if (rtDW.IntegOnlyF2S_semaphoreTaken == 0) {

for (i = 0; i < 20; i++) {

rtDW.IntegOnlyF2S_Buffer0[i] = rtU.In2[i];

}

}

/* End of RateTransition: '<Root>/IntegOnlyF2S' */

}

/* Model step function for TID1 */

void MultirateMultitaskingRateTransitions_step1(void) /* Sample time: [0.001s, 0.0s] */

{

real_T rtb_IntegOnlyF2S[20];

real_T Integrator1_DSTATE;

real_T OutportBufferForOut3;

real_T tmp;

int32_T i;

uint32_T Algorithm_ELAPS_T;

/* RateTransition: '<Root>/IntegOnlyF2S' */

rtDW.IntegOnlyF2S_semaphoreTaken = 1;

for (i = 0; i < 20; i++) {

rtb_IntegOnlyF2S[i] = rtDW.IntegOnlyF2S_Buffer0[i];

}

rtDW.IntegOnlyF2S_semaphoreTaken = 0;

/* End of RateTransition: '<Root>/IntegOnlyF2S' */

/* FunctionCallGenerator: '<Root>/FcnCall Generator' incorporates:

* SubSystem: '<Root>/Algorithm'

*/

if (rtDW.bitsForTID1.Algorithm_RESET_ELAPS_T) {

Algorithm_ELAPS_T = 0U;

} else {

Algorithm_ELAPS_T = rtM->Timing.clockTick1 - rtDW.Algorithm_PREV_T;

}

rtDW.Algorithm_PREV_T = rtM->Timing.clockTick1;

rtDW.bitsForTID1.Algorithm_RESET_ELAPS_T = 0U;

/* DiscreteIntegrator: '<S1>/Integrator1' */

tmp = 0.001 * (real_T)Algorithm_ELAPS_T;

for (i = 0; i < 20; i++) {

/* DiscreteIntegrator: '<S1>/Integrator1' */

Integrator1_DSTATE = rtDW.Integrator1_DSTATE[i];

if (rtDW.Integrator1_SYSTEM_ENABLE == 0) {

/* DiscreteIntegrator: '<S1>/Integrator1' */

Integrator1_DSTATE += tmp * rtDW.Integrator1_PREV_U[i];

}

/* DiscreteIntegrator: '<S1>/Integrator1' */

rtDW.Integrator1_DSTATE[i] = Integrator1_DSTATE;

/* DiscreteIntegrator: '<S1>/Integrator2' */

if (rtDW.Integrator2_SYSTEM_ENABLE == 0) {

/* DiscreteIntegrator: '<S1>/Integrator2' */

rtDW.Integrator2_DSTATE[i] += tmp * rtDW.Integrator2_PREV_U[i];

}

/* End of DiscreteIntegrator: '<S1>/Integrator2' */

/* DiscreteIntegrator: '<S1>/Integrator3' */

if (rtDW.Integrator3_SYSTEM_ENABLE != 0) {

/* DiscreteIntegrator: '<S1>/Integrator3' */

OutportBufferForOut3 = rtDW.Integrator3_DSTATE[i];

} else {

/* DiscreteIntegrator: '<S1>/Integrator3' */

OutportBufferForOut3 = tmp * rtDW.Integrator3_PREV_U[i] +

rtDW.Integrator3_DSTATE[i];

}

/* End of DiscreteIntegrator: '<S1>/Integrator3' */

/* DiscreteIntegrator: '<S1>/Integrator3' */

rtDW.OutportBufferForOut3[i] = OutportBufferForOut3;

/* Update for DiscreteIntegrator: '<S1>/Integrator1' incorporates:

* RateTransition: '<Root>/DetAndIntegF2S'

*/

rtDW.Integrator1_PREV_U[i] = rtDW.DetAndIntegF2S_Buffer[i];

/* Update for DiscreteIntegrator: '<S1>/Integrator2' */

rtDW.Integrator2_PREV_U[i] = rtb_IntegOnlyF2S[i];

/* Update for DiscreteIntegrator: '<S1>/Integrator3' incorporates:

* Inport: '<Root>/In3'

*/

rtDW.Integrator3_DSTATE[i] = OutportBufferForOut3;

rtDW.Integrator3_PREV_U[i] = rtU.In3[i];

/* RateTransition: '<Root>/DetAndIntegS2F' incorporates:

* SignalConversion generated from: '<S1>/Out1'

*/

rtDW.DetAndIntegS2F_Buffer0[i] = Integrator1_DSTATE;

}

/* Update for DiscreteIntegrator: '<S1>/Integrator1' */

rtDW.Integrator1_SYSTEM_ENABLE = 0U;

/* Update for DiscreteIntegrator: '<S1>/Integrator2' */

rtDW.Integrator2_SYSTEM_ENABLE = 0U;

/* Update for DiscreteIntegrator: '<S1>/Integrator3' */

rtDW.Integrator3_SYSTEM_ENABLE = 0U;

/* End of Outputs for FunctionCallGenerator: '<Root>/FcnCall Generator' */

/* RateTransition: '<Root>/IntegOnlyS2F' incorporates:

* SignalConversion generated from: '<S1>/Out2'

*/

for (i = 0; i < 20; i++) {

/* FunctionCallGenerator: '<Root>/FcnCall Generator' incorporates:

* SubSystem: '<Root>/Algorithm'

*/

rtDW.IntegOnlyS2F_Buffer[i + (rtDW.IntegOnlyS2F_ActiveBufIdx == 0) * 20] =

rtDW.Integrator2_DSTATE[i];

/* End of Outputs for FunctionCallGenerator: '<Root>/FcnCall Generator' */

}

rtDW.IntegOnlyS2F_ActiveBufIdx = (int8_T)(rtDW.IntegOnlyS2F_ActiveBufIdx == 0);

/* End of RateTransition: '<Root>/IntegOnlyS2F' */

/* Update absolute time */

/* The "clockTick1" counts the number of times the code of this task has

* been executed. The resolution of this integer timer is 0.001, which is the step size

* of the task. Size of "clockTick1" ensures timer will not overflow during the

* application lifespan selected.

*/

rtM->Timing.clockTick1++;

}